Composition with Guarantees for High-integrity Embedded Software Components Assembly

# **Project Number 216682**

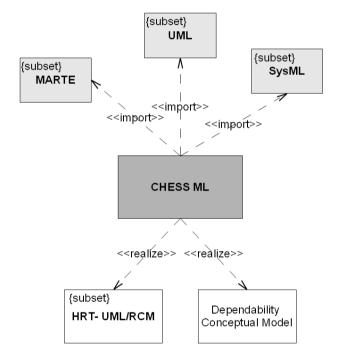

# CHESS Profile Specification V 1.3

1 March 2012

**Public Distribution**

Project Partners: Aicas, AONIX, Atos Origin, CNRI-ISTI, Enea, Ericsson, Fraunhofer, FZI, GMV

Aerospace & Defence, INRIA, Intecs, Italcertifier, Maelardalens University, Thales Alenia Space, Thales Communications, The Open Group, University of Padova , University

Polytechnic of Madrid

Every effort has been made to ensure that all statements and information contained herein are accurate, however the Partners accept no liability for any error or omission in the same.

© 2009 Copyright in this document remains vested in the CHESS Project Partners.

<sup>\*</sup> Including University of Florence (sub-contractor)

# **DOCUMENT CONTROL**

| Version | Status                                                            | Date             |

|---------|-------------------------------------------------------------------|------------------|

| 0.1     | Original input from D2.2                                          |                  |

| 0.2     | Started D2.3 and D.3.2 alignment.                                 | 11 February 2011 |

| 0.9.2   | CHESS 1.2 release                                                 | 8 May 2011       |

| 0.9.3   | CHESS 1.3 release (PIM support)                                   | 4 July 2011      |

| 1.0     | Implemented by the CHESS 2.0 toolset release                      | 3 October 2011   |

| 1.0.1   | Text editing                                                      | 21 October 2011  |

| 1.1     | Added FI4FA support, stereotypes for Simulation Based Analysis,   | 25 November 2011 |

|         | comments about hardware resource usage small (released with       |                  |

|         | CHESS 2.1 toolset)                                                |                  |

| 1.2     | Added FI4FAAnalysis stereotype, DataTypeAssign,                   | 11 January 2012  |

|         | ErrorModelAssign                                                  |                  |

|         | Added extended data types.                                        |                  |

|         | Updated Simulation-Based Timing Analysis section.                 |                  |

|         | Aligned with CHESS toolset v3.0                                   |                  |

| 1.3     | Added TransmissionWithProtocol stereotype. Added NFPConstraint    | 1 March 2012     |

|         | for deployment of multi-instances. Changed CHRtSpecification rest |                  |

|         | and BlocT multiplicities. Added MemoryPartition stereotype.       |                  |

|         |                                                                   |                  |

# TABLE OF CONTENTS

| Γa | able of Conte        | nts                              | iii  |

|----|----------------------|----------------------------------|------|

| Li | ist of Figures       |                                  | vii  |

| Li | st of Tables         |                                  | viii |

| 1  |                      | on                               |      |

| 2  |                      | ent                              |      |

| _  | -                    |                                  |      |

|    |                      | 25                               |      |

|    |                      | Requirement                      |      |

|    |                      | Derived Reqt                     |      |

| _  |                      | Satisfy                          |      |

| 3  |                      | M                                |      |

|    | 3.1 Core.            |                                  | 2    |

|    | 3.1.1 S              | Stereotypes                      |      |

|    | 3.1.1.1              |                                  |      |

|    | 3.1.1.2              | CHGaResourcePlatform             | 3    |

|    | 3.2 Views            |                                  | 3    |

|    |                      | Stereotypes                      |      |

|    | 3.2.1.1              | Requirement View                 |      |

|    | 3.2.1.2              | Component View                   |      |

|    | 3.2.1.3              | Deployment View                  |      |

|    | 3.2.1.4              | Real Time Analysis View          |      |

|    | 3.2.1.5              | Dependability Analysis View      |      |

|    |                      | onent Model                      |      |

|    |                      | Entities                         |      |

|    | 3.3.1.1              | Package                          |      |

|    | 3.3.1.2              | Realization                      |      |

|    | 3.3.1.3<br>3.3.1.4   | ClientServerPortFlowPort         |      |

|    | 3.3.1.4              | Property                         |      |

|    | 3.3.1.6              | Operation                        |      |

|    | 3.3.1.7              | Interface                        |      |

|    | 3.3.1.8              | Connector                        |      |

|    | 3.3.1.9              | PrimitiveType                    | 7    |

|    | 3.3.1.10             | <b>71</b>                        |      |

|    | 3.3.1.11             | InterfaceRealization             |      |

|    | 3.3.1.12             | Dependency                       |      |

|    | 3.3.1.13             | Enumeration                      |      |

|    | 3.3.1.14<br>3.3.1.15 | EnumerationLiteral               |      |

|    | 3.3.1.15             | Slot                             |      |

|    | 3.3.1.17             | StateMachine                     |      |

|    | 3.3.1.18             | ModeBehavior                     |      |

|    | 3.3.1.19             | Mode                             | 8    |

|    | 3.3.1.20             | ModeTransition                   | 8    |

|    | 3.3.1.21             | Configuration                    |      |

|    | 3.3.1.22             | Activity                         |      |

|    | 3.3.1.23             | Interaction                      |      |

|    | 3.3.1.24             | 8                                |      |

|    | 3.3.2 S<br>3.3.2.1   | Stereotypes                      |      |

|    | 3.3.2.1              | Component I ype                  |      |

|    |                      | Vorking with extended data types |      |

|    | 5.0.0                | 0 ··                             |      |

| 3.4 Conc  | urrency                          | 13       |

|-----------|----------------------------------|----------|

|           | Stereotypes                      |          |

| 3.4.1.1   | CHRtSpecification                | 13       |

| 3.4.1.2   | CHRtPortSlot                     | 14       |

| 3.4.1.3   | Ga_Step (TBC)                    | 15       |

| 3.5 Predi | ictability                       | 15       |

|           | Schedulability analysis.         |          |

| 3.5.1.1   | Stereotypes                      |          |

|           | Deployment configuration         |          |

| 3.5.2.1   |                                  |          |

|           | Simulation-Based Timing Analysis |          |

| 3.5.3.1   | Entities                         |          |

| 3.6 D     | ndability                        | 26       |

|           | Dependable Components            |          |

| 3.6.1.1   | Stereotypes                      | 20<br>26 |

|           | Threats And Propagation          | 20       |

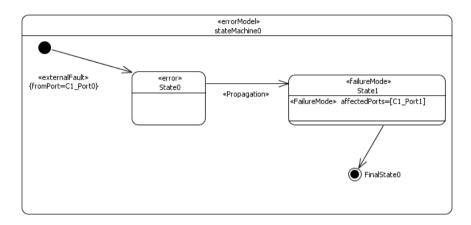

| 3.6.2.1   | ErrorModel                       |          |

| 3.6.2.1   | InternalFault                    |          |

| 3.6.2.3   | External Fault                   |          |

| 3.6.2.4   | ThreatState                      |          |

| 3.6.2.4   | Error                            |          |

|           | ErrorFree (FMEA only)            |          |

| 3.6.2.6   | UnclassifiedError (FMEA only)    |          |

| 3.6.2.7   |                                  |          |

| 3.6.2.8   | FailureMode                      |          |

| 3.6.2.9   | FailureFree (FMEA only)          |          |

| 3.6.2.10  |                                  |          |

| 3.6.2.11  | 1 8                              |          |

|           | SA profile                       |          |

|           | FMEA profile                     |          |

| 3.6.4.1   |                                  |          |

| 3.6.4.2   | ErrorModelAssign                 |          |

| 3.6.4.3   | FMEAAnalysis                     |          |

|           | State-based                      |          |

| 3.6.5.1   | StatefulHardware                 |          |

| 3.6.5.2   | StatelessHardware                |          |

| 3.6.5.3   | StatefulSoftware                 |          |

| 3.6.5.4   | StatelessSoftware                |          |

| 3.6.5.5   | FaultTolerant                    |          |

| 3.6.5.6   | RedundancyManager                |          |

| 3.6.5.7   | Variant                          |          |

| 3.6.5.8   | Adjudicator                      |          |

| 3.6.5.9   | MMActivity                       |          |

| 3.6.5.10  | 1                                |          |

| 3.6.5.11  | 1                                |          |

| 3.6.5.12  |                                  |          |

| 3.6.5.13  |                                  |          |

| 3.6.5.14  | •                                |          |

|           | Data-flow call-graph             |          |

|           | Failure propagation              |          |

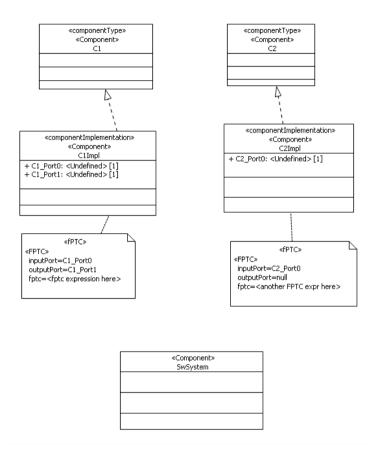

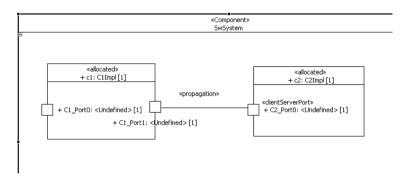

| 3.6.7.1   | FPTC                             |          |

| 3.6.7.2   | FPTCSpecification                |          |

| 3.6.7.3   | FI4FA                            |          |

| 3.6.7.4   | FI4FASpecification               |          |

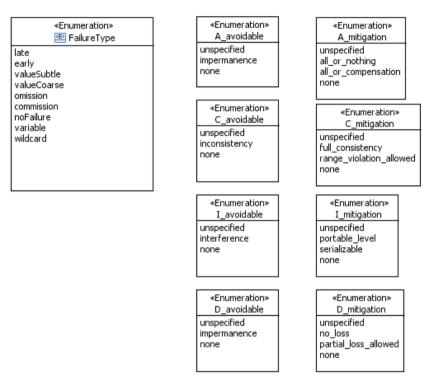

| 3.6.7.5   | ACIDAvoidable                    |          |

| 3.6.7.6   | ACIDMitigation                   |          |

| 3.6.7.7   | FPTCPortSlot                     |          |

| 3.6.7.8   | ExternalFault                    | 42       |

|                                                                                                                                                                                | .7.9 FailureMode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

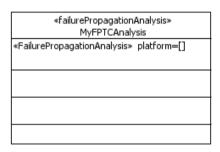

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 3.6                                                                                                                                                                            | .7.10 FailurePropagationAnalysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| 3.6                                                                                                                                                                            | .7.11 FI4FAAnalysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 3.6                                                                                                                                                                            | .7.12 DataTypes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 3.6                                                                                                                                                                            | .7.13 Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 3.6.8                                                                                                                                                                          | MitigationMeans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 3.6                                                                                                                                                                            | .8.1 TransmissionWithProtocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                         |

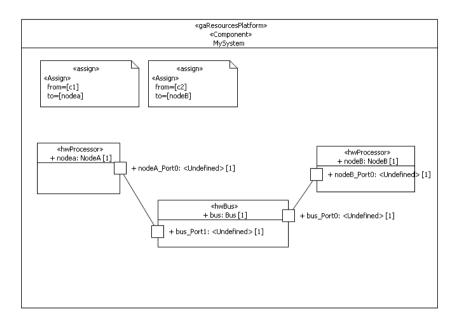

| 4 CHE                                                                                                                                                                          | SS Hardware Platform Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                                         |

|                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|                                                                                                                                                                                | Entities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 4.1.1                                                                                                                                                                          | Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 4.1.2                                                                                                                                                                          | FlowPort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 4.1.3                                                                                                                                                                          | Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| 4.1.4                                                                                                                                                                          | DataType                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 4.1.5                                                                                                                                                                          | Assign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| 4.1.6                                                                                                                                                                          | NFPConstraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                         |

| 4.2                                                                                                                                                                            | Stereotypes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                         |

| 4.2.1                                                                                                                                                                          | FIBEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| 4.2.2                                                                                                                                                                          | CH HwProcessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 4.2.3                                                                                                                                                                          | HwActuator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| 4.2.4                                                                                                                                                                          | HwSensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 4.2.5                                                                                                                                                                          | HwCache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 4.2.6                                                                                                                                                                          | HwASIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| 4.2.7                                                                                                                                                                          | MemoryPartition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 5 CHE                                                                                                                                                                          | SS PSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50                                                                         |

| 5.1                                                                                                                                                                            | CHESS Views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                                                         |

| 5.1.1                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

|                                                                                                                                                                                | Software Platform Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51                                                                         |

| Appendix                                                                                                                                                                       | A UML2 subset for CHESS ML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                                                         |

|                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| A.1                                                                                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                         |

| A.1<br>A.2                                                                                                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51<br>51                                                                   |

| A.1<br>A.2<br>A.2.1                                                                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51<br>51<br>51                                                             |

| A.1<br>A.2<br>A.2.1<br>A.2.2                                                                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3                                                                                                                                          | Introduction Classes Association Classes Power Types Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4                                                                                                                                 | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5                                                                                                                        | Introduction Classes Association Classes Power Types Dependencies Interfaces Kernel 52                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51<br>51<br>51<br>51<br>52<br>52                                           |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3                                                                                                                 | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51<br>51<br>51<br>51<br>52<br>52<br>52                                     |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1                                                                                                        | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components:                                                                                                                                                                                                                                                                                                                                                                                                                      | 51<br>51<br>51<br>51<br>52<br>52<br>52<br>53                               |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1                                                                                                        | Introduction Classes  Association Classes  Power Types  Interfaces  Kernel 52 Components  Basic Components: Composite Structures                                                                                                                                                                                                                                                                                                                                                                                                               | 51<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53                         |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4                                                                                                 | Introduction.  Classes  Association Classes.  Power Types  Dependencies  Interfaces.  Kernel 52  Components  Basic Components:  Composite Structures  InternalStructures                                                                                                                                                                                                                                                                                                                                                                       | 51<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53                         |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4<br>A.4.1                                                                                        | Introduction Classes  Association Classes  Power Types Interfaces Kernel 52 Components Basic Components: Composite Structures InternalStructures Ports 53                                                                                                                                                                                                                                                                                                                                                                                      | 51 51 51 51 51 52 52 52 53 53 53 53                                        |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.4.1<br>A.4.1<br>A.4.2<br>A.4.3                                                                             | Introduction.  Classes  Association Classes.  Power Types  Dependencies  Interfaces.  Kernel 52  Components  Basic Components:  Composite Structures  InternalStructures  Ports 53  StructuredClasses.                                                                                                                                                                                                                                                                                                                                         | 51<br>51<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53             |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4                                                                             | Introduction  Classes  Association Classes  Power Types  Interfaces  Kernel 52  Components  Basic Components:  Composite Structures  InternalStructures  Ports 53  StructuredClasses  Collaborations                                                                                                                                                                                                                                                                                                                                           | 51 51 51 51 51 51 51 51 52 52 52 52 53 53 53 53 53 53 54                   |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.4.1<br>A.4.1<br>A.4.2<br>A.4.3                                                                             | Introduction Classes  Association Classes  Power Types  Interfaces  Kernel 52 Components  Basic Components: Composite Structures InternalStructures Ports 53 StructuredClasses  Collaborations InvocationActions                                                                                                                                                                                                                                                                                                                               | 51 51 51 51 51 52 52 52 53 53 53 53 53 54 54                               |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.5                                                             | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components:  Composite Structures  InternalStructures  Ports 53  StructuredClasses  Collaborations  InvocationActions  StructuredActivities                                                                                                                                                                                                                                                                                      | 51 51 51 51 52 52 52 53 53 53 53 54 54 54                                  |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.4                                                             | Introduction Classes  Association Classes  Power Types  Interfaces  Kernel 52 Components  Basic Components: Composite Structures InternalStructures InternalStructures Ports 53 StructuredClasses  Collaborations  InvocationActions                                                                                                                                                                                                                                                                                                           | 51 51 51 51 52 52 52 53 53 53 53 54 54 54                                  |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.5                                                             | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components:  Composite Structures  InternalStructures  Ports 53  StructuredClasses  Collaborations  InvocationActions  StructuredActivities                                                                                                                                                                                                                                                                                      | 51 51 51 51 52 52 53 53 53 53 53 54 54 54                                  |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5                                             | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52  Components  Basic Components:  Composite Structures  InternalStructures  Ports 53  StructuredClasses  Collaborations  InvocationActions  StructuredActivities  Deployments                                                                                                                                                                                                                                                                        | 51 51 51 51 52 52 52 53 53 53 53 54 54 54 54                               |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.5<br>A.6                                                      | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52  Components  Basic Components:  Composite Structures  InternalStructures  Ports 53  StructuredClasses  Collaborations  InvocationActions  StructuredActivities  Deployments  Actions                                                                                                                                                                                                                                                               | 51 51 51 51 52 52 52 53 53 53 53 54 54 54 54 54                            |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.6<br>A.5<br>A.6<br>A.7                                        | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52  Components  Basic Components:  Composite Structures  InternalStructures  InternalStructures  2 Ports 53  StructuredClasses  4 Collaborations  5 InvocationActions  5 StructuredActivities  Deployments  Actions  Activities  Common Behaviours                                                                                                                                                                                                    | 51 51 51 51 51 52 52 52 53 53 53 53 54 54 54 54 54 54                      |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5<br>A.6<br>A.7<br>A.8                        | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components: Composite Structures  InternalStructures  Ports 53 StructuredClasses  Collaborations  InvocationActions  StructuredActivities Deployments Actions  Activities Common Behaviours SimpleTime                                                                                                                                                                                                                           | 51 51 51 51 51 52 52 52 53 53 53 53 54 54 54 54 54 54 54                   |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5<br>A.6<br>A.7<br>A.8                                 | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components: Composite Structures  InternalStructures  Ports 53 StructuredClasses  Collaborations  InvocationActions  StructuredActivities Deployments Actions  Activities Common Behaviours SimpleTime  Basic Behavior                                                                                                                                                                                                           | 51 51 51 51 51 52 52 52 53 53 53 53 54 54 54 54 54 54 54 54                |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5<br>A.6<br>A.7<br>A.8<br>A.8.1<br>A.8.2               | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components: Composite Structures  InternalStructures  Ports 53 StructuredClasses  Collaborations  InvocationActions  StructuredActivities Deployments Actions  Activities Common Behaviours SimpleTime  Basic Behavior                                                                                                                                                                                                           | 51 51 51 51 51 52 52 52 53 53 53 53 53 54 54 54 54 54 54 55 54             |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5<br>A.6<br>A.7<br>A.8<br>A.8.1<br>A.8.2<br>A.8.3      | Introduction Classes  Association Classes  Power Types  Dependencies  Interfaces  Kernel 52 Components  Basic Components: Composite Structures  InternalStructures  Ports 53 StructuredClasses  Collaborations  InvocationActions  StructuredActivities Deployments  Activities  Common Behaviours  SimpleTime  Basic Behavior  Communications  Communications | 51 51 51 51 51 52 52 52 53 53 53 53 53 53 54 54 54 54 54 54 54 55 55       |

| A.1<br>A.2<br>A.2.1<br>A.2.2<br>A.2.3<br>A.2.4<br>A.3<br>A.3.1<br>A.4<br>A.4.2<br>A.4.3<br>A.4.4<br>A.4.5<br>A.6<br>A.7<br>A.8<br>A.8.1<br>A.8.2<br>A.8.3<br>A.8.3             | Introduction Classes  Association Classes 2 Power Types 3 Dependencies 4 Interfaces 5 Kernel 52 Components 1 Basic Components: Composite Structures 2 Ports 53 3 StructuredClasses 4 Collaborations 5 InvocationActions 5 StructuredActivities Deployments Actions Activities Common Behaviours SimpleTime 2 Basic Behavior 3 Communications Interactions Interactions State Machines                                                                                                                                                          | 51 51 51 51 51 52 52 52 53 53 53 53 53 53 54 54 54 54 54 54 54 55 55 55    |

| A.1<br>A.2<br>A.2.1<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5<br>A.6<br>A.7<br>A.8<br>A.8.3<br>A.8.3<br>A.9<br>A.10<br>A.10 | Introduction Classes  Association Classes  Power Types Dependencies Interfaces Kernel 52 Components Basic Components: Composite Structures InternalStructures Ports 53 StructuredClasses Collaborations InvocationActions StructuredActivities Deployments Actions Activities Common Behaviours SimpleTime Basic Behavior State Machines Interactions State Machines  1 BehaviorStateMachine                                                                                                                                                   | 51 51 51 51 51 52 52 52 53 53 53 53 53 54 54 54 54 54 54 54 55 55 55 56    |

| A.1<br>A.2<br>A.2.1<br>A.2.3<br>A.2.4<br>A.2.5<br>A.3<br>A.3.1<br>A.4<br>A.4.3<br>A.4.4<br>A.4.5<br>A.4.6<br>A.5<br>A.6<br>A.7<br>A.8<br>A.8.3<br>A.8.3<br>A.9<br>A.10<br>A.10 | Introduction Classes  Association Classes 2 Power Types 3 Dependencies 4 Interfaces 5 Kernel 52 Components 1 Basic Components: Composite Structures 2 Ports 53 3 StructuredClasses 4 Collaborations 5 InvocationActions 5 StructuredActivities Deployments Actions Activities Common Behaviours SimpleTime 2 Basic Behavior 3 Communications Interactions Interactions State Machines                                                                                                                                                          | 51 51 51 51 51 52 52 52 53 53 53 53 53 54 54 54 54 54 54 54 55 55 55 56 56 |

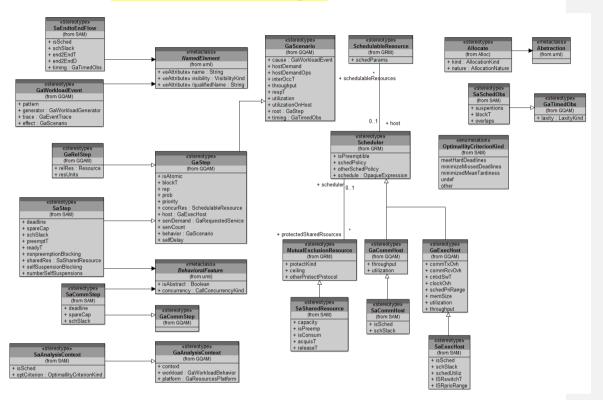

| B.1   Core Elements (CoreElements)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Appendix 1     | B MARTE Subset for CHESS ML                                                                             | 57  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------|-----|

| B.3   High-Level Application Modeling (HLAM)   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                                                                                                         |     |

| B.4   Analysis Modelling (GQAM and SAM) (UPM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B.2            | Generic Component Model (GCM)                                                                           | 58  |

| Appendix C  C.1 ModelElement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B.3            |                                                                                                         |     |

| Appendix C  C.1 ModelElement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\mathbf{B.4}$ | Analysis Modelling (GQAM and SAM) (UPM)                                                                 | 58  |

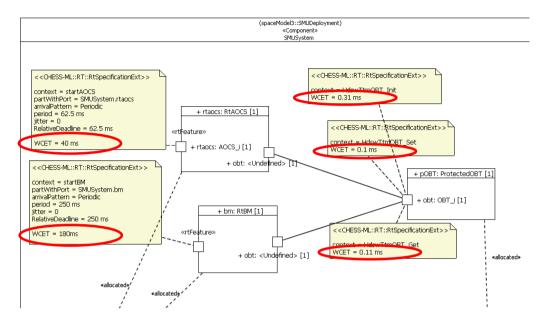

| C.2       Blocks 63         C.3       Ports and Flows       6         C.4       Constraint Blocks       6         C.5       Activities       6         C.6       Requirements       6         Appendix D       An investigation about UML deferred event support in CHESS       6         D.1       Introduction       6         D.2       UML State Machine Deferred Events       6         D.3       Use Cases       6         D.4       Deferred event: which concern?       6         D.5       Modeling Deferred Event through Functional View       6         D.6       Modelling Deferred Event by inheritance in the Non Functional e View       6         D.7       Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines       6         D.8       Conclusion       6         Appendix E       Modeling operation WCET and transferred data       7         E.1       Extending the MARTE RtSpecification stereotype       7                                                                         | Appendix       |                                                                                                         |     |

| C.3         Ports and Flows.         6           C.4         Constraint Blocks.         6           C.5         Activities.         6           C.6         Requirements.         6           Appendix D         An investigation about UML deferred event support in CHESS.         6           D.1         Introduction.         6           D.2         UML State Machine Deferred Events.         6           D.3         Use Cases.         6           D.4         Deferred event: which concern?         6           D.5         Modeling Deferred Event through Functional View.         6           D.6         Modeling Deferred Event by inheritance in the Non Functional e View.         6           D.7         Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines.         6           D.8         Conclusion.         6           Appendix E         Modeling operation WCET and transferred data         7           E.1         Extending the MARTE RtSpecification stereotype.         7 | C.1            | ModelElement                                                                                            | 63  |

| C.4 Constraint Blocks 6 C.5 Activities 6 C.6 Requirements 6 Appendix D An investigation about UML deferred event support in CHESS 6 D.1 Introduction 6 D.2 UML State Machine Deferred Events 6 D.3 Use Cases 6 D.4 Deferred event: which concern? 6 D.5 Modeling Deferred Event through Functional View 6 D.6 Modeling Deferred Event by inheritance in the Non Functional e View 6 D.7 Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines 6 D.8 Conclusion 6 Appendix E Modeling operation WCET and transferred data 7 E.1 Extending the MARTE RtSpecification stereotype 7                                                                                                                                                                                                                                                                                                                                                                                                                                | C.2            | Blocks 63                                                                                               |     |

| C.5         Activities         6           C.6         Requirements         6           Appendix D         An investigation about UML deferred event support in CHESS         6           D.1         Introduction         6           D.2         UML State Machine Deferred Events         6           D.3         Use Cases         6           D.4         Deferred event: which concern?         6           D.5         Modeling Deferred Event through Functional View         6           D.6         Modeling Deferred Event by inheritance in the Non Functional e View         6           D.7         Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines         6           D.8         Conclusion         6           Appendix E         Modeling operation WCET and transferred data         7           E.1         Extending the MARTE RtSpecification stereotype         7                                                                                                                | C.3            | Ports and Flows                                                                                         | 63  |

| C.6 Requirements 6  Appendix D An investigation about UML deferred event support in CHESS 6  D.1 Introduction 6  D.2 UML State Machine Deferred Events 6  D.3 Use Cases 6  D.4 Deferred event: which concern? 6  D.5 Modeling Deferred Event through Functional View 6  D.6 Modeling Deferred Event by inheritance in the Non Functional e View 6  D.7 Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines 6  D.8 Conclusion 6  Appendix E Modeling operation WCET and transferred data 7  E.1 Extending the MARTE RtSpecification stereotype 7                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C.4            | Constraint Blocks                                                                                       | 63  |

| Appendix D An investigation about UML deferred event support in CHESS 6  D.1 Introduction 6  D.2 UML State Machine Deferred Events 6  D.3 Use Cases 6  D.4 Deferred event: which concern? 6  D.5 Modeling Deferred Event through Functional View 6  D.6 Modeling Deferred Event by inheritance in the Non Functional e View 6  D.7 Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines 6  D.8 Conclusion 6  Appendix E Modeling operation WCET and transferred data 7  E.1 Extending the MARTE RtSpecification stereotype 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C.5            | Activities                                                                                              | 63  |

| D.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C.6            |                                                                                                         |     |

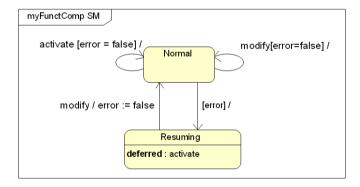

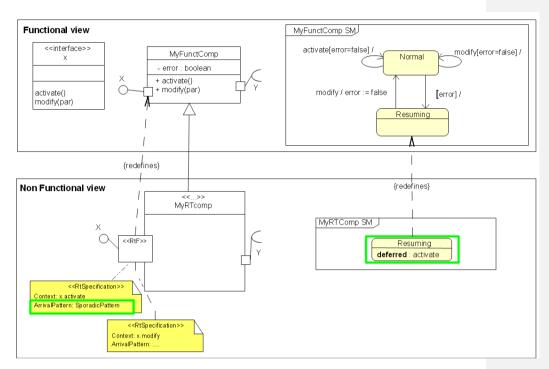

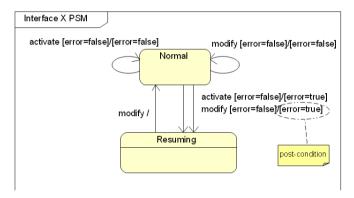

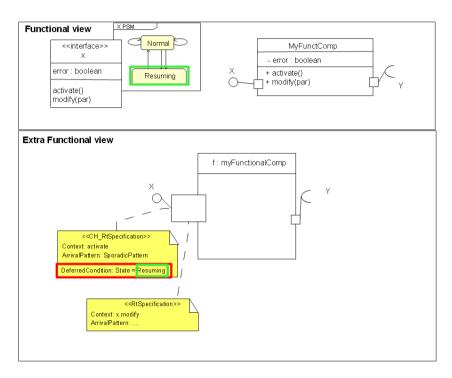

| D.2 UML State Machine Deferred Events 6 D.3 Use Cases 6 D.4 Deferred event: which concern? 6 D.5 Modeling Deferred Event through Functional View 6 D.6 Modeling Deferred Event by inheritance in the Non Functional e View 6 D.7 Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines 6 D.8 Conclusion 6 Appendix E Modeling operation WCET and transferred data 7 E.1 Extending the MARTE RtSpecification stereotype 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Appendix 1     | An investigation about UML deferred event support in CHESS                                              | 64  |

| D.3 Use Cases 6 D.4 Deferred event: which concern? 6 D.5 Modeling Deferred Event through Functional View 6 D.6 Modeling Deferred Event by inheritance in the Non Functional e View 6 D.7 Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines 6 D.8 Conclusion 6 Appendix E Modeling operation WCET and transferred data 7 E.1 Extending the MARTE RtSpecification stereotype 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D.1            | Introduction                                                                                            | 64  |

| D.4 Deferred event: which concern? 6 D.5 Modeling Deferred Event through Functional View 6 D.6 Modeling Deferred Event by inheritance in the Non Functional e View 6 D.7 Modelling deferred events as interface operation decorations in the Extra Functional view: using Protocol State Machines 6 D.8 Conclusion 6 Appendix E Modeling operation WCET and transferred data 7 E.1 Extending the MARTE RtSpecification stereotype 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D.2            | UML State Machine Deferred Events                                                                       | 64  |

| D.5 Modeling Deferred Event through Functional View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D.3            |                                                                                                         |     |