# Memoria centrale a semiconduttore (Cap. 5 – Stallings)

| Memory Type                            | Category           | Erasure                   | Write Mechanism | Volatility  |

|----------------------------------------|--------------------|---------------------------|-----------------|-------------|

| Random-access<br>memory (RAM)          | Read-write memory  | Electrically, byte-level  | Electrically    | Volatile    |

| Read-only<br>memory (ROM)              | Read-only memory   | Not possible              | Masks           |             |

| Programmable<br>ROM (PROM)             |                    |                           | Electrically    | Nonvolatile |

| Erasable PROM<br>(EPROM)               | Read-mostly memory | UV light, chip-level      |                 |             |

| Electrically Erasable<br>PROM (EEPROM) |                    | Electrically, byte-level  |                 |             |

| Flash memory                           |                    | Electrically, block-level |                 |             |

Architettura degli elaboratori -1

Pagina 187

Operazioni cella memoria

Control

Select

Cell

Data in

Select

Cell

Sense

(a) Write

(b) Read

Architettura degli elaboratori -1

Pagina 189

## Memorie a semiconduttore

- RAM

- Accesso casuale

- Read/Write

- Volatile

- Memorizzazione temporanea

- Statica o dinamica

Architettura degli elaboratori -1

Pagina 188

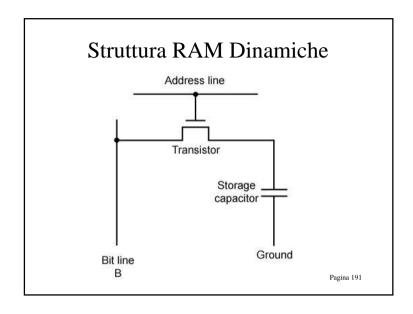

# RAM Dinamiche (Dynamic RAM)

- Bit memorizzati come cariche in condensatori

- Decadimento delle cariche con il tempo

- Necessitano di refresh delle cariche, anche durante l'alimentazione

- Costruzione più semplice

- Un condensatore per bit

- · Meno costose

- Necessitano di circuiti per il refresh

- · Più lente

- Usate per la memoria principale

- · In essenza operano in modo analogico

- il livello di carica determina il valore digitale

Architettura degli elaboratori -1

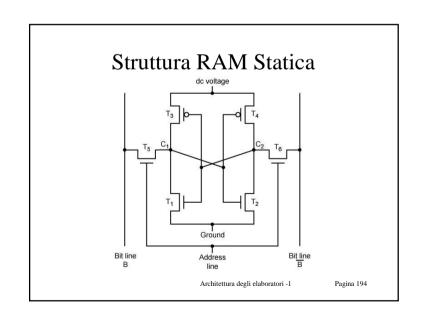

# **RAM Statica**

- Bit memorizzati tramite porte logiche

- Nessuna perdita di carica

- Nessuna necessità di refresh

- Costruzione più complessa

- Più elementi per bit

- Più costosa

- Non ha bisogno di circuiti di refresh

- Più veloci

- Usate per la cache

- Digitale

- usa flip flop

Architettura degli elaboratori -1

Pagina 193

## Funzionamento DRAM

- Linea indirizzo attivata quando si deve scrive o legge un bit

- Transistor "chiuso" (la corrente fluisce)

- Write

- Si applica tensione alla linea di bit

- Tensione alta indica valore 1; tensione bassa indica valore 0

- Poi si applica un segnale alla linea indirizzo

- · Trasferisce la carica al condensatore

- Read

- Si seleziona la linea indirizzo

- · transistor si accende

- La carica del condensatore fluisce attraverso la linea di bit verso un amplificatore

- Valore di carica comparato con un segnale di riferimento per stabilire se vale 0 o 1

- La carica del condensatore deve essere ristabilita (refresh)

Architettura degli elaboratori -1

#### Funzionamento RAM Statica

- La disposizione dei transistor garantisce stati stabili

- · Stato 1

- C<sub>1</sub> alto, C<sub>2</sub> basso

- T<sub>1</sub> T<sub>4</sub> "spenti", T<sub>2</sub> T<sub>3</sub> "accesi",

- State 0

- C2 alto, C1 basso

- T<sub>2</sub> T<sub>3</sub> "spenti", T<sub>1</sub> T<sub>4</sub> "accesi",

- La linea indirizzo controlla i transistor T<sub>5</sub> T<sub>6</sub> (accesi con presenza di segnale)

- Write si applica il valore da scrivere alla linea B ed il complemento del valore alla linea B

- Read il value viene letto tramite la linea B

Architettura degli elaboratori -1

Pagina 195

# Read Only Memory (ROM)

- Memorizzazione permanente

- Non volatili

- Usate per memorizzare:

- microprogrammi

- subroutine di libreria

- programmi di sistema (BIOS)

- funzioni tabulate

Architettura degli elaboratori -1

Pagina 197

#### SRAM e DRAM a confronto

- · Entrambe sono volatili

- Alimentazione necessaria per preservare i dati

- · celle dinamiche

- Più semplici da costuire, più piccole

- Più dense

- Meno costose

- Necessitano di refresh

- Unità di memoria più capienti

- · celle statiche

- Più veloci

- Cache

Architettura degli elaboratori -1

Pagina 196

# Tipi di ROM

- Scritte in produzione

- Molto costoso per pochi "pezzi"

- Programmabili (ona sola volta)

- PROM

- Necessitano di strumentazione speciale per la programmazione

- Principalmente di lettura (Read "mostly")

- Erasable Programmable (EPROM)

- Si cancellano (per intero) tramite raggi ultravioletti

- Electrically Erasable (EEPROM)

- · Impiegano molto più tempo per la scrittura che per la lettura

- Memorie Flash

- · Cancellazione elettrica di blocchi di memoria

Architettura degli elaboratori -1

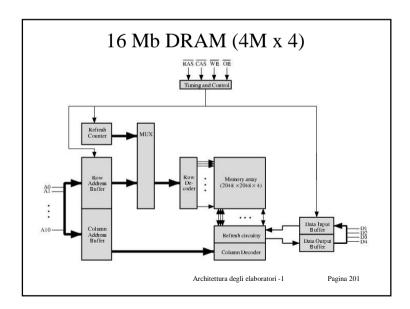

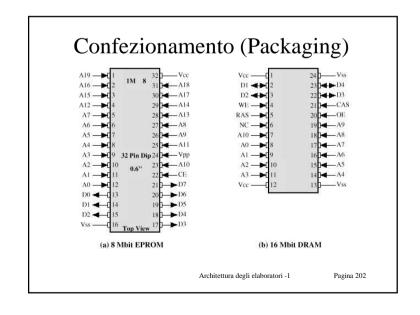

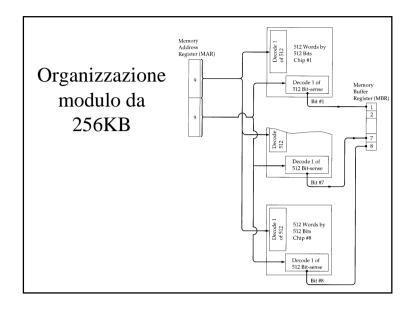

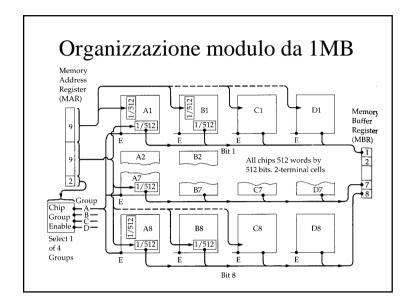

# Organizzazione DRAM

- Un chip da 16Mbit può essere organizzato come un 1M di parole da 16 bit

- Alternativamente si hanno 16 chip da 1Mbit, dove il primo bit della parola si trova nel primo chip, il secondo bit nel secondo chip e così via

- Un chip da 16Mbit può essere organizzato come un array di 2048 x 2048 x 4 bit

- Riduce il numero di pin di indirizzamento

- Multiplex per l'indirizzamento per righe e colonne

- 11 pin per l'indirizzo (2<sup>11</sup>=2048)

- L'aggiunta di un pin raddoppia l'intervallo di valori e quindi quadruplica la capacità indirizzabile

Architettura degli elaboratori -1

Pagina 199

# Refreshing

- Circuiti di refresh inclusi nel chip di memoria

- Chip disabilitato durante il refresh

- Un contatore di refresh genera in sequenza tutti gli indirizzi di riga

- Quindi si legge il valore e lo si riscrive nella locazione

- Tale operazione consuma tempo

- Rallenta le prestazioni

Architettura degli elaboratori -1

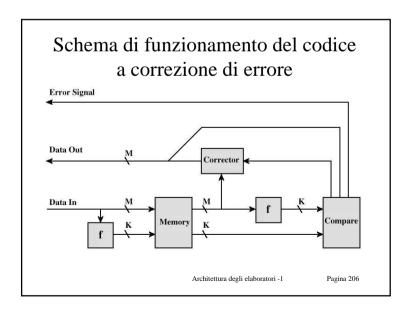

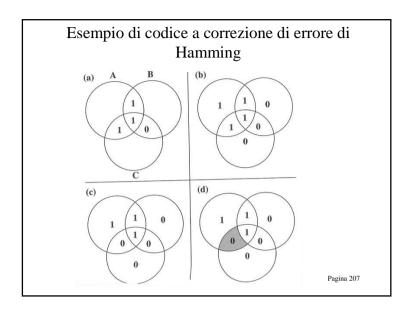

## Correzione Errori

- Guasti Hardware (Hard Failure)

- Guasti permanenti

- Errori Software (Soft Error)

- Random, non-distruttivi

- Danni alla memoria non permanenti

- Errori rilevati ed eventualmente corretti usando, ad esempio, codici correttori di Hamming

Architettura degli elaboratori -1

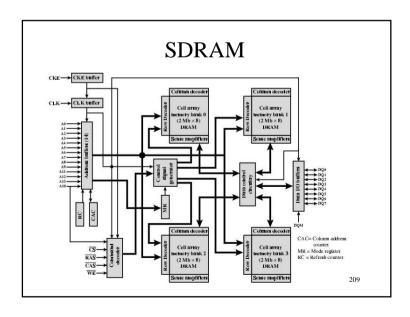

# DRAM Sincrona (SDRAM)

- Accesso sincronizzato con un clock esterno

- Indirizzo presentato alla RAM

- La RAM recupera i dati (usualmente la CPU si pone in attesa)

- Poiché la SDRAM sposta i dati in sincronia con il clock di sistema, la CPU sa quando i dati saranno pronti

- La CPU non deve attendere, può svolgere altre attività

- Il "Burst mode" permette alla SDRAM di predisporre un flusso di dati e di spedirlo in output in blocchi

- La DDR-SDRAM invia i dati due volte per ciclo di clock (sia durante il fronte di ascesa che di discesa del segnale di clock)

Architettura degli elaboratori -1

Pagina 208

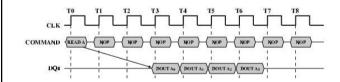

# Temporizzazione della lettura SDRAM

Figure 5.13 SDRAM Read Timing (Burst Length = 4, CAS latency = 2)

Architettura degli elaboratori -1

#### DDR SDRAM

- SDRAM può inviare i dati solo una volta per ciclo di clock

- Double-Data-Rate SDRAM può inviare i dati due volte per ciclo

- "rising edge" e "falling edge"

Architettura degli elaboratori -1

Pagina 211

# Diagramma RAMBUS Controller RDRAM 1 RDRAM 2 ... RDRAM n NCT(7:6) RCRA(2) TCR.(2) TCR.(2) TCR.(2) TCR.(2) TCR.(2) TCR.(2) TCR.(2) TCR.(2) TCR.(3) TCR.(4) TCR.(4) TCR.(4) TCR.(4) TCR.(4) TCR.(5) TCR.(6) TCR

#### **RAMBUS**

- Adottata da Intel per Pentium & Itanium

- "Avversario" principale della SDRAM

- package verticale tutti i pin su un lato

- Dati scambiati tramite 28 cavi

- Il bus indirizza fino a 320 chip RDRAM alla velocità di 1.6 Gbps

- Protocollo di trasferimento dei blocchi asincrono

- Tempo di accesso 480ns

- poi trasferimento dati a 1.6 Gbps

Architettura degli elaboratori -1

Pagina 212

## Cache DRAM

- · Prodotta da Mitsubishi

- Integra una piccola cache SRAM (16 kb) all'interno di un generico chip DRAM

- Usata come una cache vera e propria

- Linee a 64 bit

- Efficace per accessi casuali

- Oppure di supporto per l'accesso seriale a blocchi di dati

- Ad esempio, per il refresh di uno schermo bit napped

- CDRAM può precaricare dati da DRAM in SRAM

- Successivamente si effettua accesso sequenziale esclusivamente alla SRAM

Architettura degli elaboratori -1