#### Soluzione: valutazione delle prestazioni

- Per rispondere alla domanda bisogna calcolare il rapporto tra le prestazioni di una pipeline a 4 stadi senza stalli con le prestazioni della pipeline con ritardi

- Le prestazioni di una pipeline a 4 stadi senza ritardi si ottengono considerando la formula data con *k*=4 e 0 cicli di stallo:

$$\frac{1}{1+0}4=4$$

- · Per calcolare le prestazioni in presenza di stalli bisogna calcolare:

- la probabilità di eseguire una delle istruzioni di salto

salto incondizionato  $\rightarrow$  0,01 perché 1 su 100 è un salto incondizionato salto condizionato preso  $\rightarrow$  0,15\*0,6 = 0,09 perché 15 istr. su 100, e il 60% salta salto condizionato non preso  $\rightarrow$  0,15\*0,4 = 0,06 perché 15 istr. su 100, e il 40% non salta

- la frazione di cicli di stallo per tipo di istruzione di salto

vedi prossimi lucidi

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 76

#### Soluzione: valutazione delle prestazioni

· Stalli per salto condizionato preso

|                |    |           | cicli clo | <u>ck</u>  |        |   |

|----------------|----|-----------|-----------|------------|--------|---|

| istr. eseguita | 1  | 2         | 3         | 4          | 5      | 6 |

| branch         | IF | ID        | EI        | WO         |        |   |

| i + 1          |    | Œ         | stallo    | IF         | ID     |   |

| i + 2          |    |           | stallo    | stallo     | IF     |   |

| i + 3          |    |           |           | stallo     | stallo |   |

|                |    | quindi si | i hanno 2 | cicli di s | tallo  |   |

Stalli per salto condizionato non preso

| •              |    | •     | cicli clo         | ck       |        |   |

|----------------|----|-------|-------------------|----------|--------|---|

| istr. eseguita | 1  | 2     | 3                 | 4        | 5      | 6 |

| branch         | IF | ID    | EI                | WO       |        |   |

| i + 1          |    | IF    | stallo            | ID       | EI     |   |

| i + 2          |    |       | stallo            | IF       | ID     |   |

| i + 3          |    |       |                   | stallo   | IF     |   |

|                |    | quino | li si ha <b>1</b> | ciclo di | stallo |   |

Introduzione, Struttura e funzione CPU Architettura degli elaboratori -1

Pagina 78

#### Soluzione: valutazione delle prestazioni

oiali alaak

· Stalli per salto incondizionato

|                |    |                 | CICII CIOC | /K     |    |   |

|----------------|----|-----------------|------------|--------|----|---|

| istr. eseguita | 1  | 2               | 3          | 4      | 5  | 6 |

| jump           | IF | ID              | EI         | wo     |    |   |

| i + 1          |    | )x <del>(</del> | IF         | ID     | EI |   |

| i + 2          |    |                 | stallo     | IF     | ID |   |

| i + 3          |    |                 |            | stallo | IF |   |

quindi si ha 1 ciclo di stallo

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 77

## Soluzione: valutazione delle prestazioni

• la frazione di cicli in cui si ha stallo è:

• e quindi le prestazioni della pipeline con stalli è:

$$S_k = \frac{1}{1+0,25} 4 = 3, 2$$

Concludendo, la risposta al quesito è  $4/3,2 = 1,25 \rightarrow 25\%$

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

#### Principali Innovazioni nei Computer (1)

- Il concetto di famiglia

- IBM System/360, anno 1964

- DEC PDP-8

- Separa l'architettura dall'implementazione

- Unità di Controllo Microprogrammata

- Idea iniziale di Wilkes, anno 1951

- Introdotta nell' IBM System/360, anno 1964

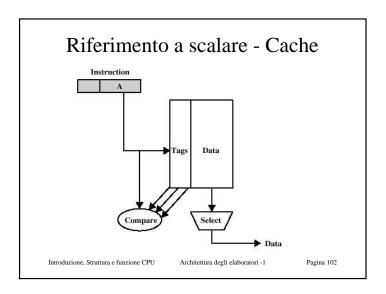

- Memoria Cache

- IBM System/360 model 85, anno 1969

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 80

### Passo successivo - RISC

- Reduced Instruction Set Computer

- Caratteristiche chiave

- Numero elevato di registri ad uso generale

- ... oppure utilizzo di compilatori per ottimizzare l'uso dei registri

- Set istruzioni semplice e limitato

- Ottimizzazione della pipeline (basata sul formato fisso per le istruzioni, metodi indirizzamento semplici,...)

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 82

### Principali Innovazioni nei Computer (2)

- · RAM a Semiconduttori

- anno 1970

- Microprocessori

- Intel 4004, anno 1971

- Pipeline

- già vista a lezione

- Processori Multipli

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 81

## Comparazione fra vari processori

|                                         |                | dex Instruction<br>ISC)Comput |                | Reduced In<br>Set (RISC) |               |               | Superscalar    |                |

|-----------------------------------------|----------------|-------------------------------|----------------|--------------------------|---------------|---------------|----------------|----------------|

| Characteristic                          | IBM<br>370/168 | VAX<br>11/780                 | Intel<br>80486 | SPARC                    | MIPS<br>R4000 | PowerPC       | Ultra<br>SPARC | MIPS<br>R10000 |

| Year developed                          | 1973           | 1978                          | 1989           | 1987                     | 1991          | 1993          | 1996           | 1996           |

| Number of<br>instructions               | 208            | 303                           | 235            | 69                       | 94            | 225           |                |                |

| Instruction size (bytes)                | 2-6            | 2-57                          | 1-11           | - 4                      | 4             | 48            | 4              | 4              |

| Addressing modes                        | 4              | 22                            | 11             | I.                       | 1             | 2             | 1              | 1              |

| Number of general-<br>purpose registers | 16             | 16                            | 8              | 40 - 520                 | 32            | 32            | 40 - 520       | 32             |

| Control memory size<br>(Kbits)          | 420            | +80                           | 246            | 100                      | Esse.         | i <del></del> | रहा:           | 8-8            |

| Cache size (KBytes)                     | 64             | 64                            | 8              | 32                       | 128           | 16-32         | 32             | 64             |

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

# Perchè erano nate le architetture Complex Istruction Set Computer (CISC) ?

- Costo del software molto maggiore del costo dell' hardware

- Linguaggi ad alto livello sempre più complessi

- Gap semantico

#### conseguenze:

- Set di istruzioni ampio

- Svariati modi di indirizzamento

- Implementazione hardware di costrutti di linguaggi ad alto livello

- Ad esempio: CASE (switch) su VAX

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 84

# Studio delle caratteristiche di esecuzione delle istruzioni

- Operazioni eseguite

- determinano le funzioni da eseguire e le modalità di interazione con la memoria

- · Operandi usati

- tipo e frequenza determinano le modalità di salvataggio e i modi di indirizzamento

- · Serializzazione dell'esecuzione

- determina l'organizzazione della pipeline e del controllo

- Studi sviluppati a partire dalle istruzioni macchina generate dai programmi scritti in un linguaggio ad alto livello

- Utilizzate misure dinamiche raccolte durante l'esecuzione di programmi

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 86

## Scopi del CISC

- Facilitare la scrittura del compilatore

- Migliorare l'efficienza dell' escuzione

- Operazioni complesse implementate tramite microcodice

- Supportare i linguaggi ad alto livello più complessi

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 85

## Operazioni

- Assignamento

- Trasferimento di dati

- Costrutti condizionali (IF, LOOP)

- Controllo di serializzazione

- Chiamata/ritorno da procedura impiega molto tempo

- Alcuni costrutti dei linguaggi ad alto livello richiedono molte operazioni macchina

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -l

# Frequenza relativa di istruzioni ad alto livello [PATT82a]

|        | Occorrenza Dinamica |     | correnza Dinamica Occorrenza ponderata sulle istruzioni macchina |     | sugli a | a ponderata<br>ccessi a<br>noria |

|--------|---------------------|-----|------------------------------------------------------------------|-----|---------|----------------------------------|

|        | Pascal              | С   | Pascal                                                           | С   | Pascal  | С                                |

| ASSIGN | 45%                 | 38% | 13%                                                              | 13% | 14%     | 15%                              |

| LOOP   | 5%                  | 3%  | 42%                                                              | 32% | 33%     | 26%                              |

| CALL   | 15%                 | 12% | 31%                                                              | 33% | 44%     | 45%                              |

| IF     | 29%                 | 43% | 11%                                                              | 21% | 7%      | 13%                              |

| GOTO   | _                   | 3%  | -                                                                | _   | _       | _                                |

| OTHER  | 6%                  | 1%  | 3%                                                               | 1%  | 2%      | 1%                               |

### Chiamate di Procedura

- Consumano molto tempo

- Dipendono dal numero di parametri passati

- Dipendono dal livello di annidamento

- La maggior parte dei programmi non eseguono chiamate multiple annidate di procedure

- La maggior parte delle variabili sono locali

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 90

## Operandi

- Principalmente variabili scalari locali

- L'ottimizzazione si deve concentrare sull'accesso alle variabili locali

|                   | Pascal | С   | Media |

|-------------------|--------|-----|-------|

| Costanti Intere   | 16%    | 23% | 20%   |

| Variabili scalari | 58%    | 53% | 55%   |

| Array/Strutture   | 26%    | 24% | 25%   |

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 89

## Implicazioni

Il miglior supporto si ottiene ottimizzando le caratteristiche più utilizzate e più onerose dal punto di vista del consumo di tempo

- Ampio numero di registri o loro uso ottimizzato dal compilatore

- Ottimizzazione dei riferimenti agli operandi

- 2. Progettazione accurata della pipeline

- · Predizione dei salti condizionali, etc.

- 3. Set istruzioni semplificato (ridotto)

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

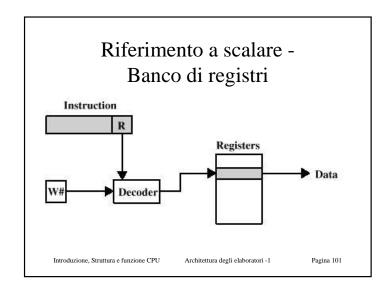

## Trattamento dei registri

- · Soluzione hardware

- Usare più registri

- In questo modo si possono mantenere più variabili nei registri

- Soluzione software

- Registri allocati dal compilatore

- Allocazione basata sulle variabili più usate per ogni intervallo di tempo

- Richiede l'utilizzo di tecniche di analisi dei programmi molto sofisticate

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 92

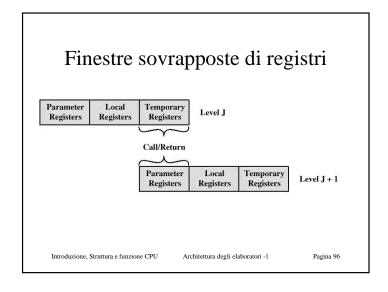

## Finestre di registri

- Osservazioni: tipicamente le chiamate di procedura

- coinvolgono pochi parametri (< 6 nel 98% dei casi)</li>

- non presentano grado di annidamento elevato

- Suggerisce la seguente soluzione: usare molti gruppi (con cardinalità limitata) di registri:

- una chiamata di procedura seleziona automaticamente un nuovo gruppo di registri

- il ritorno da una procedura (ri)seleziona il gruppo di registri assegnato precedentemente alla procedura chiamante

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 94

## Registri per variabili locali

- <u>Strategia</u>: memorizzare variabili scalari locali nei registri

- Vantaggio: riduce l'accesso alla memoria

- Problemi:

- ogni chiamata a procedure (o funzione) cambia la località (scope delle variabili)

- si devono passare i parametri della chiamata

- al ritorno dalla procedura si devono ritornare i risultati

- si devono ripristinare (i valori del)le variabili del programma chiamante al ritorno della procedura

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 93

## Finestre di registri

- Ogni gruppo di registri suddiviso in tre sottogruppi

- registri che contengono i parametri passati alla procedura chiamata

- registri che memorizzano il contenuto delle variabili locali alla procedura

- registri temporanei

- i registri temporanei di un gruppo si sovrappongono perfettamente con quelli che contengono i parametri del gruppo successivo (cioè, sono fisicamente gli stessi registri)

- Questo permette il passaggio dei parametri senza spostare i dati

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

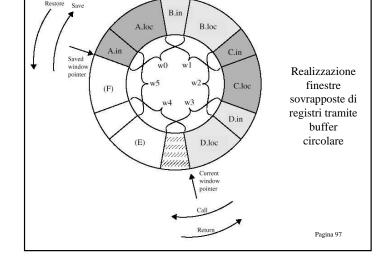

## Operazioni sul buffer circolare

- Quando avviene una chiamata, il puntatore alla finestra corrente (Current Window Pointer) viene aggiornato per mostrare la finestra di registri corrente attiva

- Se si esaurisce la capacità del buffer (tutte le finestre sono in uso a causa di chiamate annidate), viene generata una interruzione e la finestra più "vecchia" viene salvata in memoria principale

- Un puntatore (Saved Window Pointer) indica dove si deve ripristinare l'ultima finestra salvata in memoria principale

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 98

## Variabili globali

- Vengono allocate dal compilatore nella memoria

- scelta inefficiente per variabili riferite frequentemente

- Soluzione: utilizzare un gruppo di registri per memorizzare le variabili globali

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

| Banco di Registri                                                         | Cache                                                                         |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Ampio                                                                     |                                                                               |

| Tutti gli scalari locali                                                  | Scalari locali utilizzati di recente                                          |

| Variabili individuali                                                     | Blocchi di memoria                                                            |

| Variabili globali assegnate da compilatore                                | Variabili globali usate di recente                                            |

| Save/Restore basato sulla<br>profondità di annidamento<br>delle procedure | Save/Restore basato<br>sull'algoritmo di sostituzione<br>adottato dalla cache |

| Indirizzamento a registro                                                 | Indirizzamento a memoria                                                      |

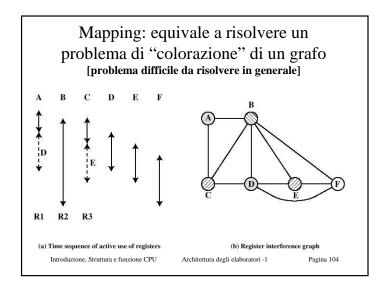

# Ottimizzazione dei registri tramite compilatore

- Assume un numero limitato di registri (16 32)

- · L'ottimizzazione è lasciata al compilatore

- Linguaggi ad alto livello non fanno riferimento esplicito ai registri

eccezione in C: register int

- Il compilatore assegna un registro simbolico (o virtuale) ad ogni variabile candidata...

- ...quindi mappa (un numero virtualmente illimitato di) registri simbolici su registri reali del processore

- Registri simbolici il cui uso non si sovrappone temporalmente possono condividere lo stesso registro reale, cioè possono essere mappati sullo stesso registro reale

- Se i registri reali non sono sufficienti per contenere tutte le variabili riferite in un dato intervallo di tempo, alcune variabili vengono mantenute in memoria principale

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

### Valutazione critica del CISC

- Semplifica il compilatore ?

- Controverso ...

- Istruzioni macchina complesse difficili da sfruttare

- Ottimizzazione più difficile

- Programmi più piccoli ?

- I programmi occupano meno memoria, ma ...

- La memoria è diventata economica

- Possono non occupare meno bit, ma semplicemente sembrano più corti in forma simbolica (codice mnemonico)

- numero maggiore di istruzioni → codici operativi più lunghi

- · riferimenti a registri richiedono meno bit ...

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 106

## Colorazione di un grafo

- Dato un grafo, costituito da nodi connessi da archi...

- ...si assegni un colore per ogni nodo, in modo tale che

- nodi adiacenti (connessi da un arco) abbiano colori diversi

- Si usi il numero minore possibile di colori

- Nel nostro caso, i nodi corrispondono a registri simbolici

- Due registri che sono "in vita" all'interno di uno stesso frammento di codice sono connessi da un arco

- Idea di fondo: colorare il grafo con n colori, dove n è il numero di registri reali

- Nodi che non possono essere colorati sono memorizzati in memoria principale

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 105

#### Valutazione critica del CISC

- Esecuzione dei programmi più veloce ?

- Si tende ad usare instruzioni più semplici

- Unità di controllo più complessa

- Controllo microprogrammato necessita di più spazio ...

- ... e quindi le istruzioni più semplici (e più usate) diventano più lente

- Non è ovvio che una architettura CISC sia la soluzione migliore

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

#### Caratteristiche RISC

- Un'istruzione per ciclo

- Operazioni da registro a registro

- Pochi e semplici modi di indirizzamento

- Pochi e semplici formati per le istruzioni

- Formati fissi per le istruzioni

- Controllo cablato (hardware, meno flessibile ma più veloce) e non microprogrammato (più flessibile ma meno veloce)

- Maggior utilizzo della ottimizzazione a livello del compilatore

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 108

### Controversia tra RISC e CISC

- Criterio quantitativo

- Paragonare dimensione dei programmi e loro velocità

- Criterio qualitativo

- Esame del merito nel supportare linguaggi ad alto livello o l'ottimizzazione dell'area di integrazione del chip

- Problemi

- Non esistono architetture RISC e CISC che siano direttamente confrontabili

- Non esiste un set completo di programmi di test

- Difficoltà nel separare gli effetti dovuti all'hardware rispetto a quelli dovuti al compilatore

- Molti confronti sono stati svolti su macchine prototipali e semplificate e non su macchine commerciali

- Molte CPU commerciali utilizzano idee provenienti da entrambe le filosofie

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 110

#### RISC "contro" CISC

- Non emerge un "vincitore" netto

- Molti processori utilizzano idee da entrambe le filosofie:

- ad esempio, PowerPC e Pentium II

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 109

# Esempio di architettura RISC: famiglia MIPS

- Riferimenti bibliografici: Stallings + Hennessy & Patterson

- Architettura molto regolare con insieme di istruzioni semplice e compatto

- Architettura progettata per una implementazione efficiente della pipeline (lo vedremo più avanti)

- Codifica delle istruzioni omogenea: 32 bit

- Co-processore per istruzioni a virgola mobile e gestione delle eccezioni

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

#### **MIPS**

#### Registri

- 32 registri di 32 bit (registro 0 contiene sempre il valore 0)

- Architettura Load / Store

- Istruzioni di trasferimento per muovere i dati tra memoria e registri

- Istruzioni per la manipolazione di dati operano sui valori dei registri

- Nessuna operazione memoria ↔ memoria

- Quindi: le istruzioni operano su registri (registro i riferito con \$i)

- Esempio: add \$0, \$1, \$2

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 112

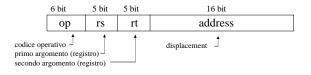

#### **MIPS**

#### Formato Istruzioni

- 32 bit per tutte, 3 formati diversi (formato R, formato I, formato J)

- Formato R (registro)

#### **MIPS**

#### Dati e modi di indirizzamento

- Registri possono essere caricati con byte, mezze parole, e parole (riempiendo con 0 quando necessario o estendendo, cioè replicando, il segno sui bit non coinvolti del registro)

- Modalità di indirizzamento ammesse (con campi di 16 bit):

- Immediata es. add \$2, \$2, 0004

- Displacement es. sw \$1,000c(\$1)

- Altre modalità derivabili:

- Indiretta registro (displacement a 0) es. sw \$2,0000(\$3)

- Assoluta (registro 0 come registro base) es. lw \$1,00c4(\$0)

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 113

#### **MIPS**

#### Formato Istruzioni

Formato I (istruzioni load / store)

Es: **0x8D2804B0** (**1w \$8, 1200(\$9)** [R8]  $\leftarrow$  Mem[1200+[R9]])

op rs At address

100011 01001 01000 0000 0100 1011 0000

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

#### **MIPS**

#### Formato Istruzioni

• Formato J (istruzioni jump)

Es: 0x0800AFFE ( j 45054 [PC] - 45054 )

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 116

## Fasi (MIPS)

#### **ID** (instruction decode/register fetch cycle):

- $A \leftarrow Regs[rs]$ ;

- $B \leftarrow Regs[rt]$ ;

- Imm  $\leftarrow$  campo immediato di IR con segno esteso ;

Dove A, B, Imm sono registri temporanei

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 118

## Fasi (MIPS)

Fasi senza pipeline:

#### **IF** (istruction fetch):

- IR  $\leftarrow$  Mem[PC];

- NPC  $\leftarrow$  PC + 4;

Dove NPC è un registro temporaneo

PC è il program counter

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 117

## Fasi (MIPS)

#### **EX** (execution/effective address cycle):

- 1. Riferimento a memoria

- $\bullet \quad ALUOutput \leftarrow A + Imm \; ;$

- 2. Istruzione ALU registro-registro

- ALUOutput  $\leftarrow$  A func B;

- ${\it 3. \ Istruzione \ ALU \ registro-immediato}$

- ALUOutput  $\leftarrow$  A op Imm;

shift a sinistra

- 4. Salto

- ALUOutput  $\leftarrow$  NPC + (Imm << 2);

- Cond  $\leftarrow$  (A = = 0);

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -l

## Fasi (MIPS)

#### **MEM** (memory access/branch completion cycle):

• PC ← NPC; in tutti i casi

#### 1. Riferimento a memoria

- LMD ← Mem[ALUOutput] or Mem[ALUOutput] ← B;

- 2. Salto

- if (Cond)  $PC \leftarrow ALUOutput$ ;

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 120

## Fasi (MIPS)

#### WB (write/back cycle):

- 1. Istruzione ALU registro-registro

- Regs[rd] ← ALUOutput;

- 2. Istruzione ALU registro-immediato

- Regs[rt] ← ALUOutput;

- 3. Istruzione Load

- Regs[rt]  $\leftarrow$  LMD;

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

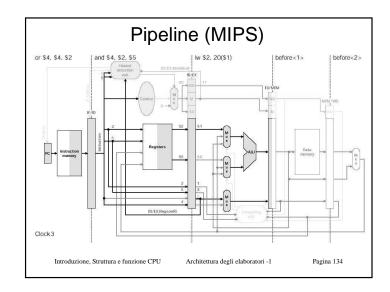

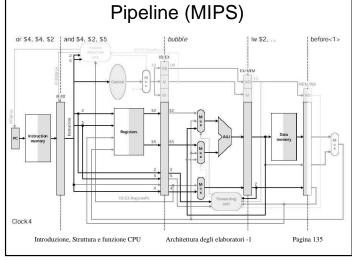

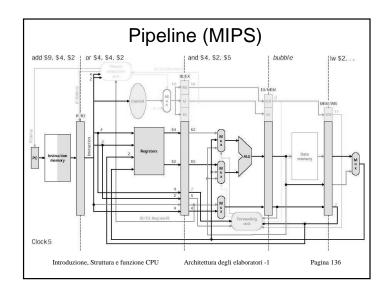

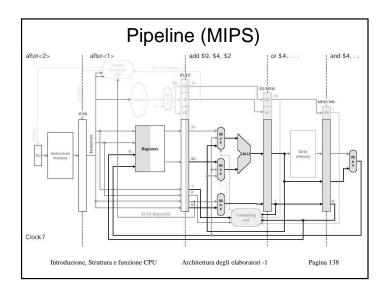

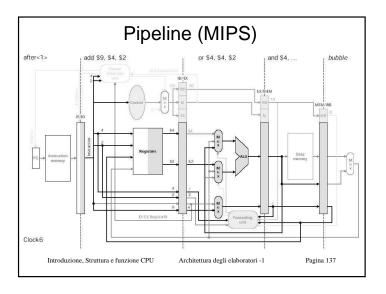

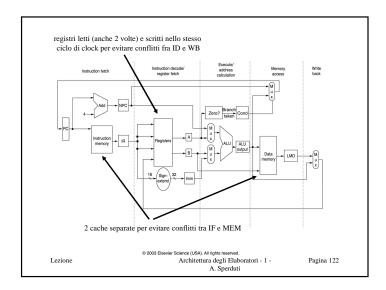

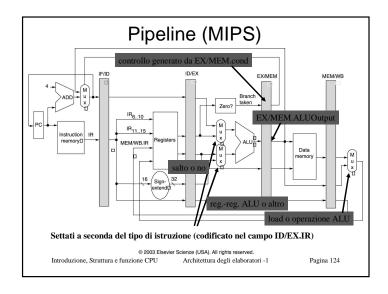

## Pipeline (MIPS)

- Architettura che si presta ad una facile introduzione della pipeline: uno stadio per fase, 1 ciclo di clock per stadio

- Occorre memorizzare i dati fra una fase e la successiva: si introducono opportuni registri (denominati pipeline registers o pipeline latches) fra i vari stadi della pipeline

- Tali registri memorizzano sia dati che segnali di controllo che devono transitare da uno stadio al successivo

- Dati che servono a stadi non immediatemente successivi vengono comunque copiati nei registri dello stato successivo per garantire la correttezza dei dati

Lezione

Architettura degli Elaboratori - 1 -A. Sperduti Pagina 123

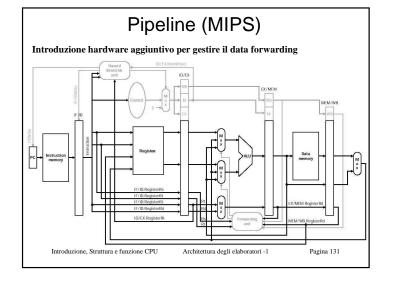

## Pipeline (MIPS)

- Quando una istruzione passa dalla fase ID a quella EX si dice che la istruzione è stata "rilasciata" (issued)

- Nella Pipeline MIPS è possibile individuare tutte le dipendenze dai dati nella fase ID

- Se si rileva una dipendenza dai dati per una istruzione, questa va in stallo prima di essere rilasciata

- Inoltre, sempre nella fase ID, è possibile determinare che tipo di data forwarding adottare per evitare lo stallo ed anche predisporre gli opportuni segnali di controllo

- Vediamo di seguito come realizzare un forwarding nella fase EX per una dipendenza di tipo RAW (Read After Write) con sorgente che proviene da una istruzione load (load interlock)

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 126

| Stage | Any instruction                                                     |                                                                                                                |                                                  |

|-------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| IF    | <pre>IF/ID.IR ← Mem[PC] IF/ID.NPC,PC ← (if ((EX else {PC+4});</pre> | /MEM.opcode == branch) お花 F                                                                                    | EX/MEM.cond) {EX/MEM.ALUOutput                   |

| ID    | <pre>ID/EX.NPC \( IF/ID.NPC;</pre>                                  | [rs]]; ID/EX.B ← Regs[IF/I<br>ID/EX.IR ← IF/ID.IR;<br>(IF/ID.IR[immediate field]                               |                                                  |

|       | ALU instruction                                                     | Load or store instruction                                                                                      | Branch instruction                               |

| EX    | EX/MEM.IR ID/EX.IR;<br>EX/MEM.ALUUutput<br>ID/EX.A op ID/EX.B;      | EX/MEM.IR — ID/EX.IR;<br>EX/MEM.ALUOutput —<br>ID/EX.A + ID/EX.Imm;                                            | EX/MEM.ALUOutput — ID/EX.NPC + (ID/EX.Imm << 2); |

|       | or<br>EX/MEM.ALUOutput ←<br>ID/EX.A op ID/EX.Inm;                   | EX/MEM.B ← ID/EX.B                                                                                             | EX/MEM.cond ← (ID/EX.A<br>== 0);                 |

| MEM   | MEM/WB.IR — EX/MEM.IR;<br>MEM/WB.ALUOputput —<br>EX/MEM.ALUOutput;  | MEM/WB.IR — EX/MEM.IR;<br>MEM/WB.LMD —<br>Mem(EX/MEN.ALUOutput];<br>or<br>Mem(EX/MEM.ALUOutput)<br>— EX/MEM.B; |                                                  |

| WB    | Regs(MEM/WB.IR[rd])<br>MEM/WB.ALUOutput;<br>or                      | For load only:                                                                                                 |                                                  |

|       | Regs[MEM/WB.IR[rt]]<br>MEM/WB.ALUOutput;                            | Regs[MEM/WB.IR[rt]] ←<br>MEM/WB.LMD;                                                                           |                                                  |

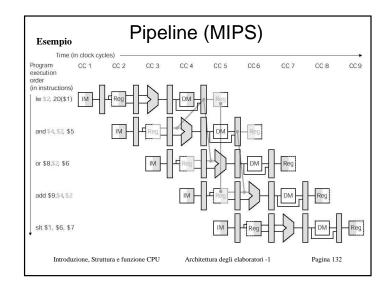

## Pipeline (MIPS)

#### Possibili casi

| Situazione                               | Esempio di codice                                                                       | Azione                                                                                                                                    |

|------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Nessuna dipendenza                       | LD <b>\$1</b> , 45(\$2)<br>DADD \$5, \$6, \$7<br>DSUB \$8, \$6, \$7<br>OR \$9, \$6, \$7 | Non occorre fare nulla perché nor<br>c'è dipendenza rispetto alle 3<br>istruzioni successive                                              |

| Dipendenza che richiede uno stallo       | LD \$1, 45(\$2)<br>DADD \$5, \$1, \$7<br>DSUB \$8, \$6, \$7<br>OR \$9, \$6, \$7         | Opportuni comparatori rilevano<br>l'uso di \$1 in DADD ed evitano i<br>rilascio di DADD                                                   |

| Dipendenza risolvibile con un forwarding | LD \$1, 45(\$2)<br>DADD \$5, \$6, \$7<br>DSUB \$8, \$1, \$7<br>OR \$9, \$6, \$7         | Opportuni comparatori rilevano<br>l'uso di \$1 in DSUB e inoltrano il<br>risultato della load alla ALU in<br>tempo per la fase EX di DSUB |

| Dipendenza con accessi in ordine         | LD \$1, 45(\$2)<br>DADD \$5, \$6, \$7<br>DSUB \$8, \$6, \$7<br>OR \$9, \$1, \$7         | Non occorre fare nulla perché la<br>lettura di \$1 in OR avviene dopo<br>la scrittura del dato caricato                                   |

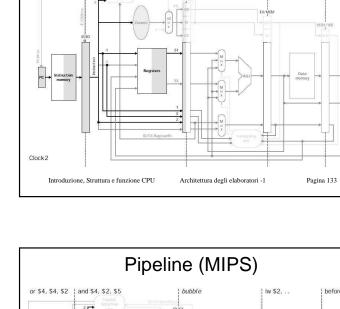

## Pipeline (MIPS)

#### Condizioni per riconoscere le dipendenze

| Opcode (ID/EX) | Opcode (IF/ID)               | Matching operand fields                                                                                |

|----------------|------------------------------|--------------------------------------------------------------------------------------------------------|

| Load           | R-R ALU                      | $\mathrm{ID}/\mathrm{EX}.\mathrm{IR}[\mathrm{rt}] == \mathrm{IF}/\mathrm{ID}.\mathrm{IR}[\mathrm{rs}]$ |

| Load           | R-R ALU                      | $\mathrm{ID}/\mathrm{EX.IR}[\mathrm{rt}] == \mathrm{IF}/\mathrm{ID.IR}[\mathrm{rt}]$                   |

| Load           | Load, Store, Imm ALU, branch | ID/EX.IR[rt] == IF/ID.IR[rs]                                                                           |

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

Pagina 128

#### Pipeline (MIPS) Pipeline register Opcode containing source of source destination Comparison (if instruction instruction instruction equal then forward) Register-register ALU, Top ALU ALU immediate, load, input EX/MEM.IR[rd] == register ALU ID/EX.IR[rs] EX/MEM.IR[rd] == ID/EX.IR[rt] EX/MEM Register-register ALU register ALU input MEM/WB Register-register ALU, Top ALU ALU immediate, load, input MEM/WB.IR[rd] == Registerregister ALU MEM/WB Register-Register-register ALU Bottom ALU register ALU EX/MEM Register-register ALU, Top ALU ALU immediate, load, input store, branch ALU EX/MEM.IR[rt] == EX/MEM Register-register ALU Bottom ALU EX/MEM.IR[rt] == immediate ID/EX.IR[rt] MEM/WB ID/EX Register-register ALU, Top ALU ALU immediate, load, input MEM/WB.IR[rt] == ID/EX.IR[rs] ALU store, branch MEM/WB ALU ID/EX Register-register ALU Bottom ALU MEM/WB.IR[rt] == immediate MEM/WB ID/EX Register-register ALU, ALU immediate, load, Top ALU input MEM/WB.IR[rt] == store, branch MEM/WB Load ID/EX Bottom ALU MEM/WB.IR[rt] == input ID/EX.IR[rt] Register-register ALU

## Pipeline (MIPS)

- La logica per decidere come effettuare il forwarding è simile a quella appena vista per individuare le dipendenze, ma considera molti più casi

- Una osservazione chiave è che i registri di pipeline contengono:

- dati su cui effettuare il forwarding

- i campi registro sorgente e destinazione

- Tutti i dati su cui effettuare il forwarding provengono:

- dall'output della ALU

- dalla memoria dati

- ... e sono diretti verso:

- l'input della ALU

- l'input della memoria dati

- il comparatore con 0

- Quindi occorre confrontare i registri destinazione di IR in EX/MEM e MEM/WB con i registri sorgente di IR in ID/EX e EX/MEM

Introduzione, Struttura e funzione CPU

Architettura degli elaboratori -1

and \$4, \$2, \$5

| lw \$2, 20(\$1)

Pipeline (MIPS)

before<2>

| before<3>