# Pipeline (MIPS)

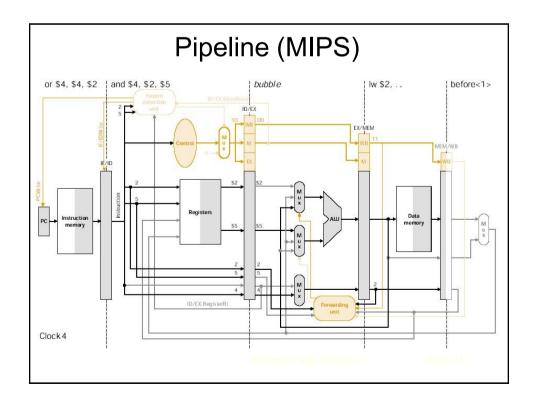

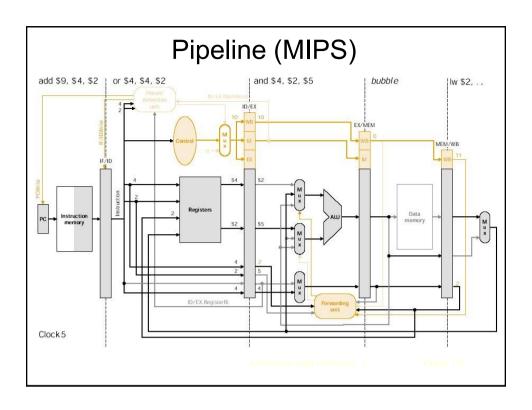

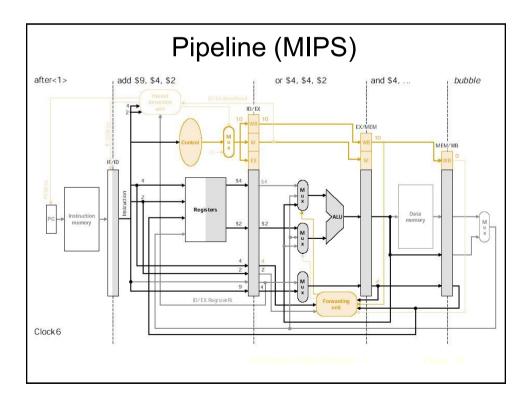

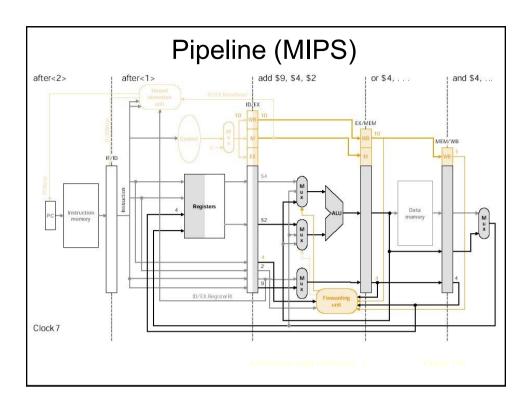

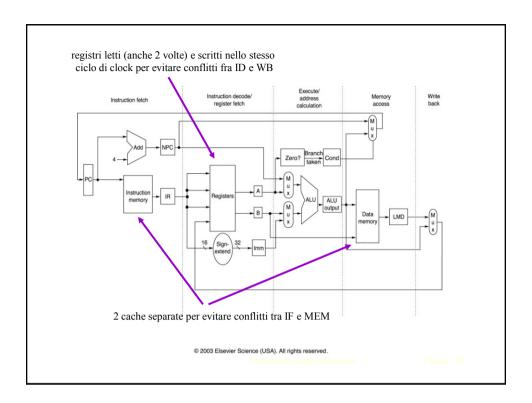

- Architettura che si presta ad una facile introduzione della pipeline: uno stadio per fase, 1 ciclo di clock per stadio

- Occorre memorizzare i dati fra una fase e la successiva: si introducono opportuni registri (denominati pipeline registers o pipeline latches) fra i vari stadi della pipeline

- Tali registri memorizzano sia dati che segnali di controllo che devono transitare da uno stadio al successivo

- Dati che servono a stadi non immediatemente successivi vengono comunque copiati nei registri dello stato successivo per garantire la correttezza dei dati

Architettura degli elaboratori -1

Pagina 145

i

| Charac | A i                                                                                                                                                                                                                                           |                                                                                                 |                                                  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| Stage  | Any instruction                                                                                                                                                                                                                               |                                                                                                 |                                                  |  |  |

| IF     | <pre>IF/ID.IR — Mem[PC] IF/ID.NPC,PC — (if ((EX/MEM.opcode == branch) &amp;&amp; EX/MEM.cond){EX/MEM.ALUOutput} else {PC+4});</pre>                                                                                                           |                                                                                                 |                                                  |  |  |

| ID     | <pre>ID/EX.A \( \text{Regs[IF/ID.IR[rs]]}; \text{ID/EX.B} \( \text{Regs[IF/ID.IR[rt]]}; \) ID/EX.NPC \( \text{IF/ID.NPC}; \text{ID/EX.IR} \( \text{IF/ID.IR}; \) ID/EX.Imm \( \text{sign-extend} \text{(IF/ID.IR[immediate field])}; \)</pre> |                                                                                                 |                                                  |  |  |

|        | ALU instruction                                                                                                                                                                                                                               | Load or store instruction                                                                       | Branch instruction                               |  |  |

| EX     | EX/MEM.IR 	— ID/EX.IR; EX/MEM.ALUOutput 	— ID/EX.A op ID/EX.B;                                                                                                                                                                                | EX/MEM.IR                                                                                       | EX/MEM.ALUOutput  ID/EX.NPC + (ID/EX.Imm  << 2); |  |  |

|        | or<br>EX/MEM.ALUOutput ←<br>ID/EX.A op ID/EX.Imm;                                                                                                                                                                                             | EX/MEM.B ← ID/EX.B                                                                              | EX/MEM.cond ← (ID/EX.A == 0);                    |  |  |

| MEM    | MEM/WB.IR — EX/MEM.IR;<br>MEM/WB.ALUOputput —<br>EX/MEM.ALUOutput;                                                                                                                                                                            | MEM/WB.IR — EX/MEM.IR; MEM/WB.LMD — Mem[EX/MEM.ALUOutput]; or Mem[EX/MEM.ALUOutput] — EX/MEM.B; |                                                  |  |  |

| WB     | Regs[MEM/WB.IR[rd]]  MEM/WB.ALUOutput; or                                                                                                                                                                                                     | For load only:                                                                                  |                                                  |  |  |

|        | Regs[MEM/WB.IR[rt]]  MEM/WB.ALUOutput;                                                                                                                                                                                                        | Regs[MEM/WB.IR[rt]] ← MEM/WB.LMD;                                                               |                                                  |  |  |

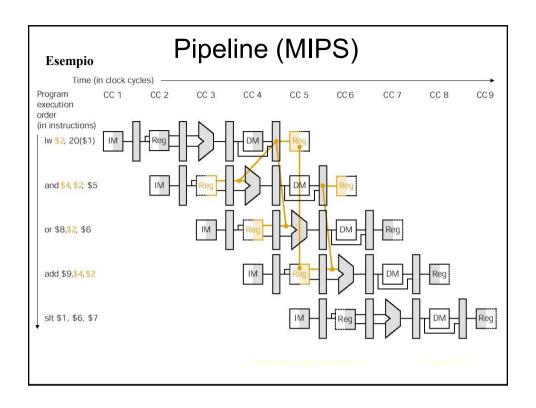

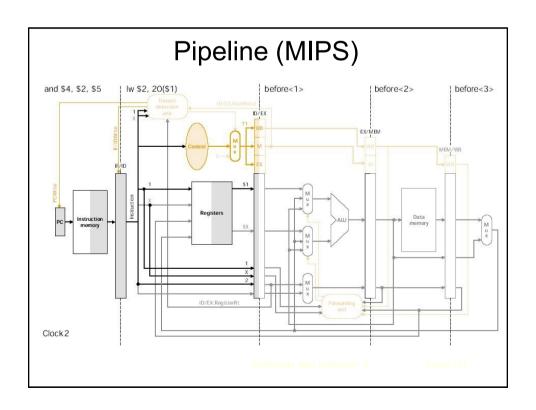

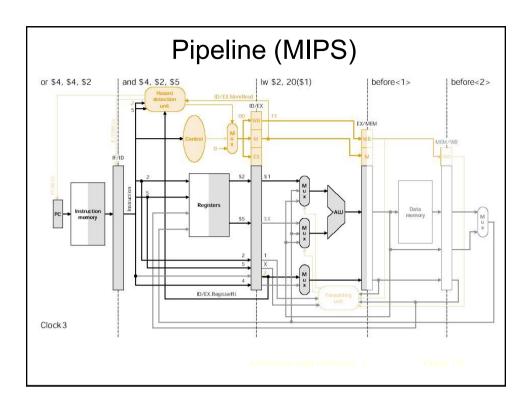

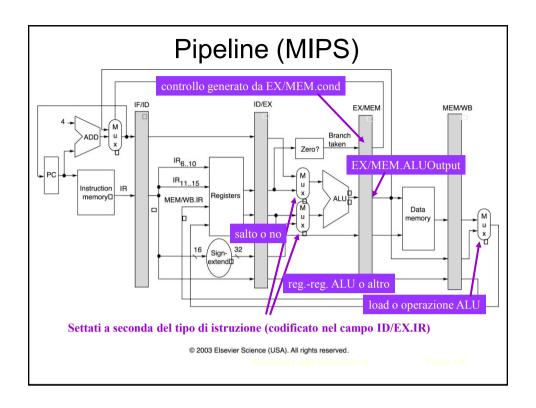

### Pipeline (MIPS)

- Quando una istruzione passa dalla fase ID a quella EX si dice che la istruzione è stata "rilasciata" (issued)

- Nella Pipeline MIPS è possibile individuare tutte le dipendenze dai dati nella fase ID

- Se si rileva una dipendenza dai dati per una istruzione, questa va in stallo prima di essere rilasciata

- Inoltre, sempre nella fase ID, è possibile determinare che tipo di data forwarding adottare per evitare lo stallo ed anche predisporre gli opportuni segnali di controllo

- Vediamo di seguito come realizzare un forwarding nella fase EX per una dipendenza di tipo RAW (Read After Write) con sorgente che proviene da una istruzione load (load interlock)

Architettura degli elaboratori -1

Pagina 14

# Pipeline (MIPS)

#### Possibili casi

| Situazione                               | Esempio di codice                                                               | Azione                                                                                                                                    |

|------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Nessuna dipendenza                       | LD \$1, 45(\$2)<br>DADD \$5, \$6, \$7<br>DSUB \$8, \$6, \$7<br>OR \$9, \$6, \$7 | Non occorre fare nulla perché non<br>c'è dipendenza rispetto alle 3<br>istruzioni successive                                              |

| Dipendenza che richiede uno stallo       | LD \$1, 45(\$2)<br>DADD \$5, \$1, \$7<br>DSUB \$8, \$6, \$7<br>OR \$9, \$6, \$7 | Opportuni comparatori rilevano<br>l'uso di \$1 in DADD ed evitano il<br>rilascio di DADD                                                  |

| Dipendenza risolvibile con un forwarding | LD \$1, 45(\$2)<br>DADD \$5, \$6, \$7<br>DSUB \$8, \$1, \$7<br>OR \$9, \$6, \$7 | Opportuni comparatori rilevano<br>l'uso di \$1 in DSUB e inoltrano il<br>risultato della load alla ALU in<br>tempo per la fase EX di DSUB |

| Dipendenza con accessi in ordine         | LD \$1, 45(\$2)<br>DADD \$5, \$6, \$7<br>DSUB \$8, \$6, \$7<br>OR \$9, \$1, \$7 | Non occorre fare nulla perché la<br>lettura di \$1 in OR avviene dopo<br>la scrittura del dato caricato                                   |

# Pipeline (MIPS)

### Condizioni per riconoscere le dipendenze

| Opcode (ID/EX) | Opcode (IF/ID)               | Matching operand fields                                                                                |

|----------------|------------------------------|--------------------------------------------------------------------------------------------------------|

| Load           | R-R ALU                      | ID/EX.IR[rt] == IF/ID.IR[rs]                                                                           |

| Load           | R-R ALU                      | $\mathrm{ID}/\mathrm{EX}.\mathrm{IR}[\mathrm{rt}] == \mathrm{IF}/\mathrm{ID}.\mathrm{IR}[\mathrm{rt}]$ |

| Load           | Load, Store, Imm ALU, branch | ID/EX.IR[rt] == IF/ID.IR[rs]                                                                           |

Architettura degli elaboratori -1

Pagina 150

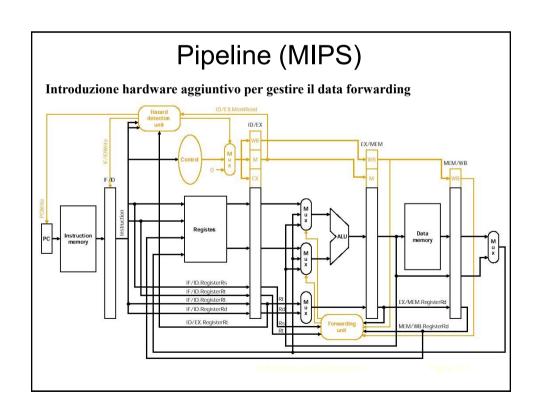

### Pipeline (MIPS)

- La logica per decidere come effettuare il forwarding è simile a quella appena vista per individuare le dipendenze, ma considera molti più casi

- Una osservazione chiave è che i registri di pipeline contengono:

- dati su cui effettuare il forwarding

- i campi registro sorgente e destinazione

- Tutti i dati su cui effettuare il forwarding provengono:

- dall'output della ALU

- dalla memoria dati

- ... e sono diretti verso:

- l'input della ALU

- l'input della memoria dati

- il comparatore con 0

- Quindi occorre confrontare i registri destinazione di IR in EX/MEM e MEM/WB con i registri sorgente di IR in ID/EX e EX/MEM

Pagina 151

| Pipeline (MIPS)                                 |                                    |                                                                  |                                                                 |                                              |                                    |  |  |

|-------------------------------------------------|------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------|------------------------------------|--|--|

| Pipeline register containing source instruction | Opcode<br>of source<br>instruction | Pipeline<br>register<br>containing<br>destination<br>instruction | Opcode of destination instruction                               | Destination<br>of the<br>forwarded<br>result | Comparison (if equal then forward) |  |  |

| EX/MEM                                          | Register-<br>register ALU          | ID/EX                                                            | Register-register ALU,<br>ALU immediate, load,<br>store, branch | Top ALU<br>input                             | EX/MEM.IR[rd] ==<br>ID/EX.IR[rs]   |  |  |

| EX/MEM                                          | Register-<br>register ALU          | ID/EX                                                            | Register-register ALU                                           | Bottom ALU<br>input                          | EX/MEM.IR[rd] ==<br>ID/EX.IR[rt]   |  |  |

| MEM/WB                                          | Register-<br>register ALU          | ID/EX                                                            | Register-register ALU,<br>ALU immediate, load,<br>store, branch | Top ALU<br>input                             | MEM/WB.IR[rd] ==<br>ID/EX.IR[rs]   |  |  |

| MEM/WB                                          | Register-<br>register ALU          | ID/EX                                                            | Register-register ALU                                           | Bottom ALU<br>input                          | MEM/WB.IR[rd] ==<br>ID/EX:IR[rt]   |  |  |

| EX/MEM                                          | ALU<br>immediate                   | ID/EX                                                            | Register-register ALU,<br>ALU immediate, load,<br>store, branch | Top ALU<br>input                             | EX/MEM.IR[rt] ==<br>ID/EX.IR[rs]   |  |  |

| EX/MEM                                          | ALU<br>immediate                   | ID/EX                                                            | Register-register ALU                                           | Bottom ALU<br>input                          | EX/MEM.IR[rt] ==<br>ID/EX.IR[rt]   |  |  |

| MEM/WB                                          | ALU<br>immediate                   | ID/EX                                                            | Register-register ALU,<br>ALU immediate, load,<br>store, branch | Top ALU<br>input                             | MEM/WB.IR[rt] ==<br>ID/EX.IR[rs]   |  |  |

| MEM/WB                                          | ALU<br>immediate                   | ID/EX                                                            | Register-register ALU                                           | Bottom ALU<br>input                          | MEM/WB.IR[rt] ==<br>ID/EX.IR[rt]   |  |  |

| MEM/WB                                          | Load                               | ID/EX                                                            | Register-register ALU,<br>ALU immediate, load,<br>store, branch | Top ALU<br>input                             | MEM/WB.IR[rt] ==<br>ID/EX.IR[rs]   |  |  |

| MEM/WB                                          | Load                               | ID/EX                                                            | Register-register ALU                                           | Bottom ALU<br>input                          | MEM/WB.IR[rt] ==<br>ID/EX.IR[rt]   |  |  |