# Modi di indirizzamento

Capitolo 11

## Vari modi di specificare l'indirizzo degli operandi

- Immediato

- Diretto

- Indiretto

- Registro

- Registro indiretto

- Spiazzamento

- Pila

## Indirizzamento immediato

- L'operando è parte dell'istruzione (campo indirizzo)

- Vantaggio: nessun accesso in M per prendere l'operando

- Svantaggio: valore limitato dalla dimensione del campo indirizzo

## Indirizzamento immediato

Istruzione

|         |          |

|---------|----------|

| Cod.Op. | Operando |

|---------|----------|

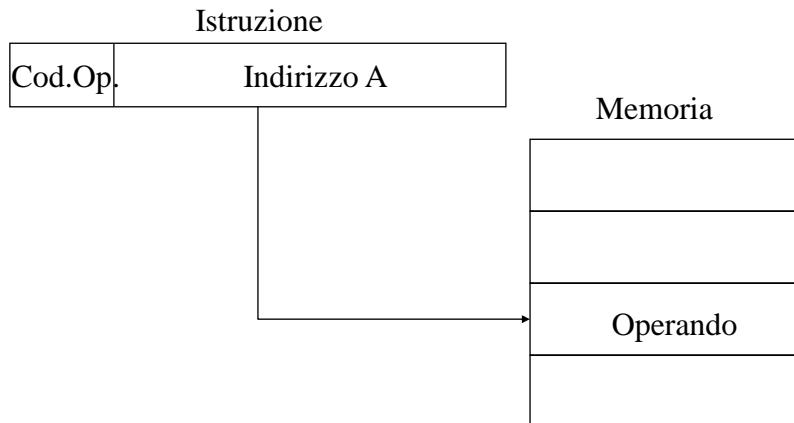

## Indirizzamento diretto

- Campo indirizzo = indirizzo dell'operando

- Esempio: ADD A

- Somma il contenuto della cella A all'accumulatore

- Bisogna andare in M all'indirizzo A per trovare l'operando

- Un singolo accesso in M per prendere l'operando

- Spazio di indirizzamento limitato

## Indirizzamento diretto

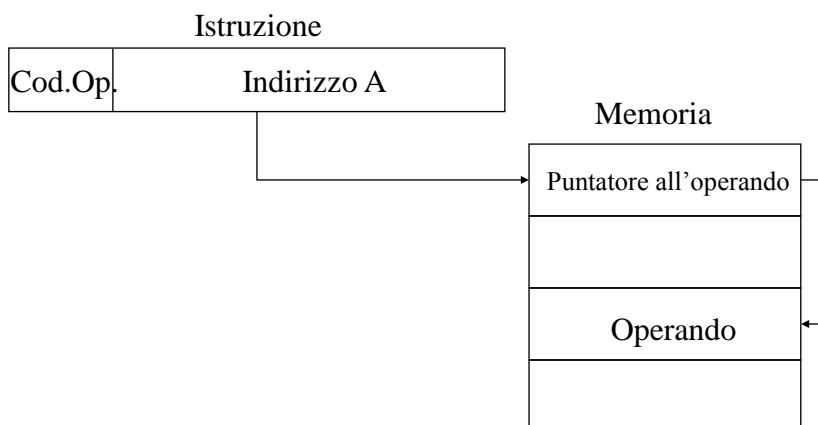

## Indirizzamento indiretto

- Il campo indirizzo contiene l'indirizzo di una cella di M, che contiene l'indirizzo dell'operando

- Vantaggio: parole di lunghezza N permettono di indirizzare  $2^N$  entità diverse

- In realtà  $2^K$ , dove K è la lunghezza del campo indirizzo

- Svantaggio: due accessi in M per ottenere l'operando

- Esempio: ADD A

- Somma il contenuto della cella puntata dal contenuto di A all'accumulatore

## Indirizzamento indiretto

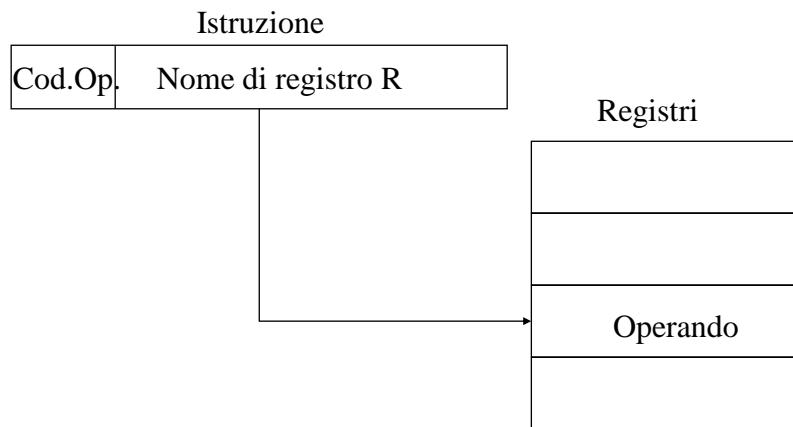

## Indirizzamento registro

- L'operando è in un registro indicato nel campo indirizzo

- Numero limitato di registri

- Pochi bit necessari per il campo indirizzo

- Istruzioni più corte

- Fase di fetch più veloce (nessun accesso in M per prendere l'operando)

## Indirizzamento registro

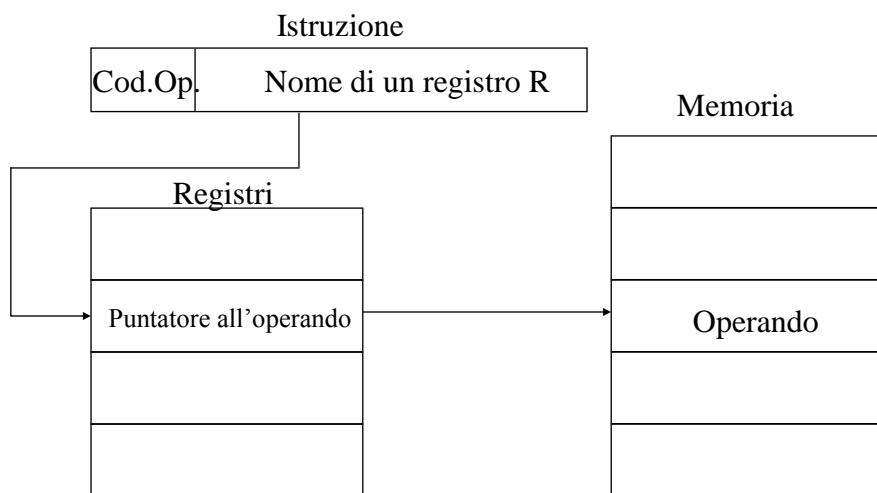

## Indirizzamento registro indiretto

- Stesso principio dell'indirizzamento indiretto

- L'operando è in una cella di M puntata dal contenuto del registro R

- Grande spazio di indirizzamento ( $2^n$ )

- Un accesso in meno in M rispetto all'indirizzamento indiretto

## Indirizzamento registro indiretto

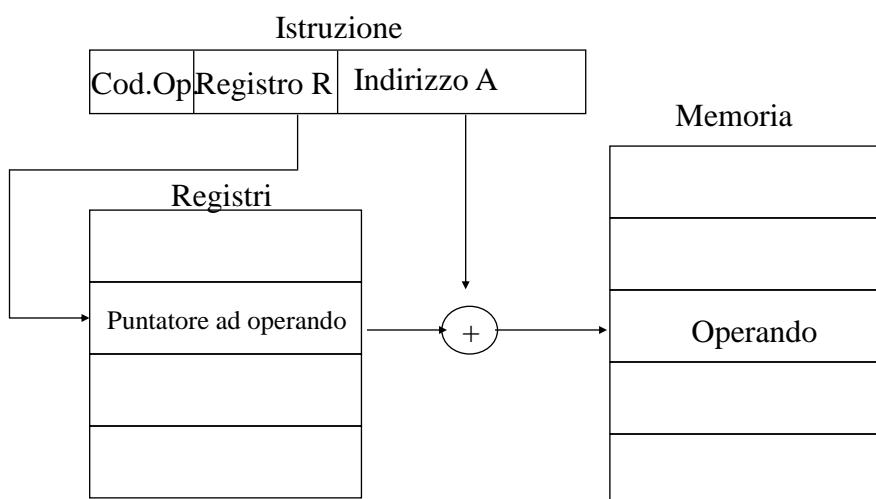

## Indirizzamento con spiazzamento

- Combinazione di indirizzamento diretto e indirizzamento registro indiretto

- Il campo indirizzo ha due sottocampi

- A = valore di base (diretto)

- R = registro che contiene l'indirizzo di un valore da sommare ad A per ottenere l'indirizzo

- o viceversa (R base e A spiazzamento)

## Indirizzamento con spiazzamento

## Indirizzamento relativo

- Una versione dell'indirizzamento con spiazzamento

- R = registro PC (program counter)

- Indirizzo dell'operando = A + (PC)

- A celle dalla cella di M puntata da PC

## Indirizzamento registro-base

- A contiene lo spiazzamento

- R contiene il puntatore all'indirizzo base

- R può essere esplicito o implicito

## Indicizzazione

- A = base

- R = spiazzamento

- Esempio: elenco di dati memorizzati in M a partire da un indirizzo A

- Per accedere a tutti, la sequenza di indirizzi è A, A+1, A+2, ...

- A viene messo nel campo indirizzo e il registro (indice) contiene 0 all'inizio e viene incrementato di 1 dopo ogni accesso

## Indirizzamento a pila

- Pila: sequenza lineare di locazioni riservate di M

- Puntatore (nel registro SP, stack pointer) con l'indirizzo della cima della pila

- L'operando è sulla cima della pila

- Quindi è un esempio di indirizzamento a registro indiretto

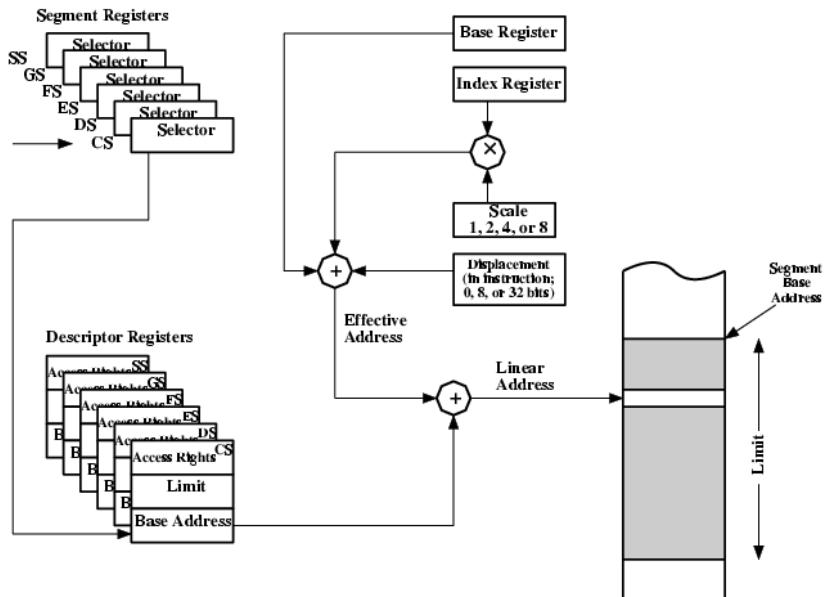

# Modi di indirizzamento del Pentium

- 12 modi di indirizzamento

- Immediato

- Registro

- Spiazzamento

- Base

- Base con spiazzamento

- Indice scalato con spiazzamento

- Indice scalato con base e spiazzamento

- Relativo

# Modi di indirizzamento del Pentium

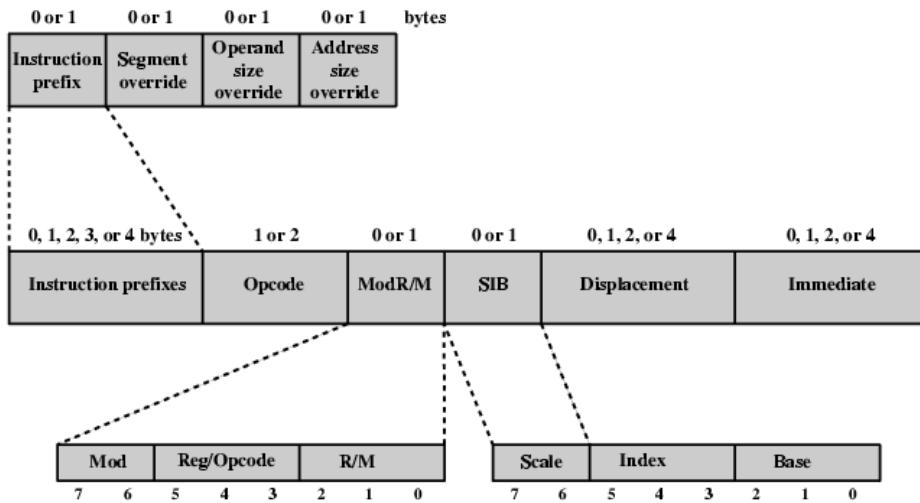

## Formato delle istruzioni

- Struttura dei campi dell'istruzione

- Include il codice operativo

- Include (in modo implicito o esplicito) uno o più operandi

- Di solito più di un formato per un linguaggio macchina

## Lunghezza delle istruzioni

- Condiziona ed è condizionata da:

- Dimensione della M

- Organizzazione della M

- Struttura del bus

- Complessità della CPU

- Velocità della CPU

- Compromesso tra repertorio di istruzioni potente e necessità di risparmiare spazio

# Allocazione dei bit

- Vari modi di indirizzamento

- Vari numeri di operandi (di solito 1 o 2)

- Registri verso M (di solito almeno 32 registri)

- Banchi di registri (esempio: Pentium ha due banchi)

- Due banchi da 8 registri ciascuno → solo 3 bit per indicare un registro (il codice operativo indica il banco)

- Intervallo di indirizzi

- Granularità degli indirizzi (es.: byte o parola)

- L'indirizzamento di byte richiede più bit ma è utile (es. per manipolare caratteri)

## Formato delle istruzioni del PDP-8

| Memory Reference Instructions |     |     |   |   | Displacement |   |

|-------------------------------|-----|-----|---|---|--------------|---|

| Opcode                        | D/I | Z/C | 4 | 5 | 6            | 7 |

| 0                             | 2   | 3   |   |   | 11           |   |

| Input/Output Instructions |   |   | Device |   | Opcode |    |

|---------------------------|---|---|--------|---|--------|----|

| 1                         | 1 | 0 | 3      | 8 | 9      | 11 |

| 0                         | 2 |   |        |   |        |    |

| Register Reference Instructions |   |   |   |                           |     |     |     |     |     |     |     |

|---------------------------------|---|---|---|---------------------------|-----|-----|-----|-----|-----|-----|-----|

| Group 1 Microinstructions       |   |   |   | Group 2 Microinstructions |     |     |     |     |     |     |     |

| 1                               | 1 | 1 | 0 | CLA                       | CLL | CMA | CML | RAR | RAL | BSW | IAC |

| 0                               | 1 | 2 | 3 | 4                         | 5   | 6   | 7   | 8   | 9   | 10  | 11  |

| Group 3 Microinstructions |   |   |   |     |     |     |     |     |     |     |    |

|---------------------------|---|---|---|-----|-----|-----|-----|-----|-----|-----|----|

| 1                         | 1 | 1 | 1 | CLA | SMA | SZA | SNL | RSS | OSR | HLT | 0  |

| 0                         | 1 | 2 | 3 | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11 |

D/I = Direct/Indirect address

IAC = Increment ACcumulator

Z/C = Page 0 or Current page

SMA = Skip on Minus Accumulator

CLA = Clear Accumulator

SZA = Skip on Zero Accumulator

CLL = Clear Link

SNL = Skip on Nonzero Link

CMA = Complement Accumulator

RSS = Reverse Skip Sense

CML = Complement Link

OSR = Or with Switch Register

RAR = Rotate Accumulator Right

HLT = HALT

RAL = Rotate Accumulator Left

MQA = Multiplier Quotient into Accumulator

BSW = Byte SWap

MQL = Multiplier Quotient Load

## Formato delle istruzioni del PDP-10

| Opcode | Register | I  | Index Register | Memory Address |    |

|--------|----------|----|----------------|----------------|----|

| 0      | 8 9      | 12 | 14             | 17 18          | 35 |

I = indirect bit

## Formato a lunghezza variabile

- Fino ad ora abbiamo visto esempi di formati a lunghezza fissa

- Alcune architetture utilizzano formati a lunghezza variabile o ibrida

Formato a lunghezza fissa

|     |                     |                     |                     |

|-----|---------------------|---------------------|---------------------|

| Op. | (Indir.) Operando 1 | (Indir.) Operando 2 | (Indir.) Operando 3 |

|-----|---------------------|---------------------|---------------------|

Formato a lunghezza variabile

|                  |                     |     |                     |

|------------------|---------------------|-----|---------------------|

| Op. e # operandi | (Indir.) Operando 1 | ... | (Indir.) Operando n |

|------------------|---------------------|-----|---------------------|

Formato ibrido

|     |                     |

|-----|---------------------|

| Op. | (Indir.) Operando 1 |

| Op. | (Indir.) Operando 1 |

## Formato delle istruzioni del PDP-11

|    |              |             |                  |   |              |        |                  |   |              |                        |                        |                      |

|----|--------------|-------------|------------------|---|--------------|--------|------------------|---|--------------|------------------------|------------------------|----------------------|

| 1  | Opcode<br>4  | Source<br>6 | Destination<br>6 | 2 | Opcode<br>7  | R<br>3 | Source<br>6      | 3 | Opcode<br>8  | Offset<br>8            |                        |                      |

| 4  | Opcode<br>8  | FP<br>2     | Destination<br>6 | 5 | Opcode<br>10 |        | Destination<br>6 | 6 | Opcode<br>12 | CC<br>4                |                        |                      |

| 7  | Opcode<br>13 |             | R<br>3           | 8 | Opcode<br>16 |        |                  | 9 | Opcode<br>4  | Source<br>6            | Destination<br>6       | Memory Address<br>16 |

| 10 | Opcode<br>7  | R<br>3      | Source<br>6      |   |              |        |                  |   |              | Memory Address<br>16   |                        |                      |

| 11 | Opcode<br>8  | FP<br>2     | Source<br>6      |   |              |        |                  |   |              | Memory Address<br>16   |                        |                      |

| 12 | Opcode<br>10 |             | Destination<br>6 |   |              |        |                  |   |              | Memory Address<br>16   |                        |                      |

| 13 | Opcode<br>4  | Source<br>6 | Destination<br>6 |   |              |        |                  |   |              | Memory Address 1<br>16 | Memory Address 2<br>16 |                      |

Numbers below fields indicate bit length

Source and Destination each contain a 3-bit addressing mode field and a 3-bit register number

FP indicates one of four floating-point registers

R indicates one of the general-purpose registers

CC is the condition code field

## Formato delle istruzioni del VAX

| Hexadecimal Format | Explanation                                                                                                                                                                               | Assembler Notation and Description                                                                                                                                                                                             |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 bits             | Opcod for RSB                                                                                                                                                                             | RSB<br>Return from subroutine                                                                                                                                                                                                  |

|                    | Opcod for CLRL<br>Register R9                                                                                                                                                             | CLRL R9<br>Clear register R9                                                                                                                                                                                                   |

|                    | Opcod for MOVW<br>Word displacement mode,<br>Register R4<br>356 in hexadecimal<br>Byte displacement mode,<br>Register R11<br>25 in hexadecimal                                            | MOVW 356(R4), 25(R11)<br>Move a word from address<br>that is 356 plus contents<br>of R4 to address that is<br>25 plus contents of R11                                                                                          |

|                    | Opcod for ADDL3<br>Short literal 5<br>Register mode R0<br>Index prefix R2<br>Indirect word relative<br>(displacement from PC)<br>Amount of displacement from<br>PC relative to location A | ADDL3 #5, R0, @ A[R2]<br>Add 5 to a 32-bit integer in<br>R0 and store the result in<br>location whose address is<br>sum of A and 4 times the<br>contents of R2<br><br>Amount of displacement from<br>PC relative to location A |

# Formato delle istruzioni del Pentium

## Formato delle istruzioni del PowerPC (1)

| ↔ 6 bits ↔ 5 bits ↔ 5 bits ↔ 16 bits → |                |        |                                         |

|----------------------------------------|----------------|--------|-----------------------------------------|

| Branch                                 | Long Immediate |        |                                         |

| Br Conditional                         | Options        | CR Bit | Branch Displacement                     |

| Br Conditional                         | Options        | CR Bit | Indirect through Link or Count Register |

(a) Branch instructions

|    |          |            |            |                    |   |

|----|----------|------------|------------|--------------------|---|

| CR | Dest Bit | Source Bit | Source Bit | Add, OR, XOR, etc. | / |

|----|----------|------------|------------|--------------------|---|

(b) Condition register logical instructions

|                |               |               |                |                      |

|----------------|---------------|---------------|----------------|----------------------|

| Ld/St Indirect | Dest Register | Base Register | Displacement   |                      |

| Ld/St Indirect | Dest Register | Base Register | Index Register | Size, Sign, Update / |

| Ld/St Indirect | Dest Register | Base Register | Displacement   |                      |

(c) Load/store instructions

## Formato delle istruzioni del PowerPC (2)

|                       |                      |                      |                       |                           |      |

|-----------------------|----------------------|----------------------|-----------------------|---------------------------|------|

| <b>Ld/St Indirect</b> | <b>Dest Register</b> | <b>Base Register</b> | <b>Displacement</b>   |                           |      |

| <b>Ld/St Indirect</b> | <b>Dest Register</b> | <b>Base Register</b> | <b>Index Register</b> | <b>Size, Sign, Update</b> | /    |

| <b>Ld/St Indirect</b> | <b>Dest Register</b> | <b>Base Register</b> | <b>Displacement</b>   |                           | XO * |

(c) Load/store instructions

|                        |                      |                      |                          |                    |                 |       |

|------------------------|----------------------|----------------------|--------------------------|--------------------|-----------------|-------|

| <b>Arithmetic</b>      | <b>Dest Register</b> | <b>Src Register</b>  | <b>Src Register</b>      | O                  | Add, Sub, etc.  | R     |

| Add, Sub, etc.         | Dest Register        | Src Register         | Signed Immediate Value   |                    |                 |       |

| <b>Logical</b>         | <b>Src Register</b>  | <b>Dest Register</b> | <b>Src Register</b>      | ADD, OR, XOR, etc. |                 |       |

| AND, OR, etc.          | Src Register         | Dest Register        | Unsigned Immediate Value |                    |                 |       |

| <b>Rotate</b>          | <b>Src Register</b>  | <b>Dest Register</b> | <b>Shift Amt</b>         | <b>Mask Begin</b>  | <b>Mask End</b> | R     |

| <b>Rotate or Shift</b> | <b>Src Register</b>  | <b>Dest Register</b> | <b>Src Register</b>      | Shift Type or Mask |                 |       |

| <b>Rotate</b>          | <b>Src Register</b>  | <b>Dest Register</b> | <b>Shift Amt</b>         | <b>Mask</b>        | XO              | S R * |

| <b>Rotate</b>          | <b>Src Register</b>  | <b>Dest Register</b> | <b>Src Register</b>      | <b>Mask</b>        | XO              | R *   |

| <b>Shift</b>           | <b>Src Register</b>  | <b>Dest Register</b> | Shift Type or Mask       |                    |                 | S R * |

(d) Integer arithmetic, logical, and shift/rotate instructions

|                    |                      |                     |                     |                     |                   |   |

|--------------------|----------------------|---------------------|---------------------|---------------------|-------------------|---|

| <b>Flt sgl/dbl</b> | <b>Dest Register</b> | <b>Src Register</b> | <b>Src Register</b> | <b>Src Register</b> | <b>Fadd, etc.</b> | R |

|--------------------|----------------------|---------------------|---------------------|---------------------|-------------------|---|

(e) Floating-point arithmetic instructions

A = Absolute or PC relative

L = Link or subroutine

O = Record overflow in XER

R = Record condition in CRI

XO = Opcode extension

S = Part of shift amount field

\* = 64-bit implementation only