### Central Processing Unit - indice

- 2 La CPU

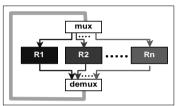

- 2.1 Logica operativa (data path)

- 2.2 Registri

- 2.3 Circuiti aritmetici dedicati

- 2.4 Arithmetic Logic Unit, ALU

- 2.5 Bus, instradatori e buffer

- 2.6 Logica di controllo (control path)

- 2.7 Set di istruzioni

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 48

#### Architettura di von Neumann 0400 - 0FFF **IP** 0100 mouse floppy hard disk 0100BE 0400<sub>XX</sub> IR xx 0401<sub>XX</sub> 0101 00 hard disk AL xx 0102 01 0402 XX video 0103 B0 0403<sub>XX</sub> T xxxx stampante :::: :: :::: :: [81] floppy xx 03FF<sub>XX</sub> 04FFxx S [82] SI xxxx hard disk ALU DB CPU Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 49

### 2. Unità centrale

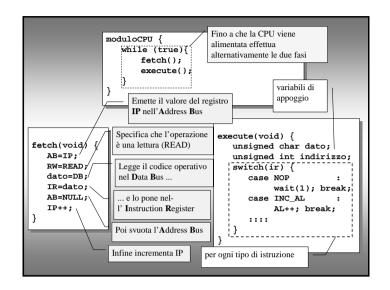

La CPU è suddivisibile in due blocchi funzionali:

- Sottosistema gestione dati: data path (logica operativa), adibito alla memorizzazione, all'elaborazione ed all'analisi dei dati interni alla CPU

- Sottosistema gestione istruzioni: control path (logica di controllo), che ha il compito di decodificare ed interpretare le istruzioni, e di far eseguire alla logica operative le operazioni necessarie per la loro esecuzione

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

### 2.1 Parte operativa (data path)

La parte operativa è costituita da vari elementi:

- Registri

- Circuiti combinatori elementari

- Arithmetic Logic Unit

- Aree di memoria di lavoro (buffer)

- Instradatori (multiplexer e demultiplexer)

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 52

### Address bus Architettura di una CPU AB buffer semplificata prefetch registro 1 reg. stack parte registro N reg. index operativa reg.stato B buffer Data Bus Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 53

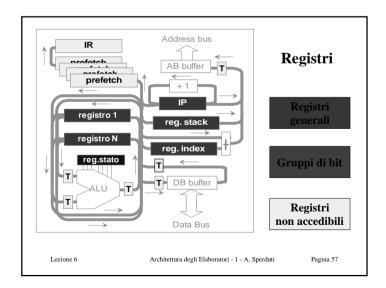

## 2.2 Registri

- Piccole memorie temporanee molto veloci basate su componenti statici (*flip flop*)

- In numero e dimensioni variabili

- Un maggior numero di registri permette di:

- Ridurre il numero di accessi alla memoria esterna

- Esecuzione più veloce

- Ridurre la complessità operativa delle istruzioni

- Compilatore più semplice

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 54

### 2.2 Registri (segue)

I registri possono avere ciascuno una funzione specifica o essere di utilizzo generale:

- **Registri dedicati** (p.es., accumulatore): ad uso limitato ma con prestazioni migliori

- Registri generali: semplificano la parte controllo e l'ottimizzazione da parte dei compilatori; facilmente scalabili

La soluzione più conveniente è quella mista

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

### 2.2 Registri (segue)

### I registri generali

- A disposizione del programmatore

- A dimensione variabile 8, 16, 32, 64 bit

- Utilizzati per la memorizzazione dati, per il calcolo di indirizzi, per operazioni aritmetico logiche

- Possono avere compiti specifici

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 56

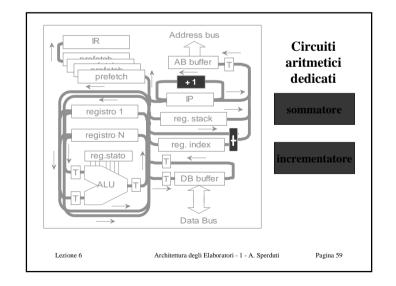

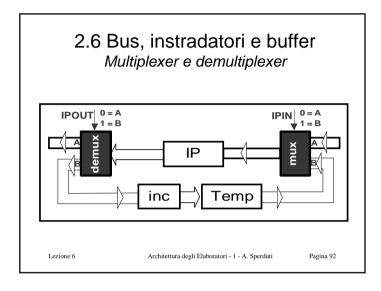

### 2.3 Circuiti aritmetici dedicati

Finalizzati esclusivamente a permettere una maggiore velocità dell'ALU, p.es.:

### • Incrementatore

- Per far avanzare l'Instruction Pointer

- Per particolari istruzioni auto-aggiornanti

### Sommatore

- Per calcolare l'indirizzo di un operando

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

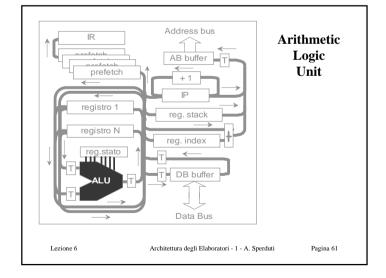

### 2.4 Arithmetic Logic Unit

- Rete combinatoria multi-funzione, in grado di effettuare operazioni aritmetiche e/o logiche su uno o due operandi

- Acquisisce ed aggiorna una serie di bit di stato, detti 'flag', p.es.: zero, carry, overflow, segno, ... (controllo residuo)

- Esegue operazioni di spostamento di bit, con shifter dedicati

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 60

### 2.4 Arithmetic Logic Unit

Codifica dei dati interi senza segno

| TIPO                           | bit | rango        |

|--------------------------------|-----|--------------|

| <b>UB</b> unsigned byte        | 8   | 0 255        |

| UW unsigned word               | 16  | 0 65525      |

| <b>UD</b> unsigned double word | 32  | $0 \sim 4GB$ |

| <b>BU</b> byte unpacked BCD    | 8   | 09           |

| <b>BP</b> byte packed BCD      | 8   | 099          |

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 62

# 2.4 Arithmetic Logic Unit *Codifiche UB, UW, UD*

Dato il numero ad **n** bit

$$A = a_{n-1} a_{n-2} \dots a_2 a_1 a_0$$

la i esima cifra ha un peso di 2i, ad esempio

$$1010_{bin} = 1x2^3 + 0x2^2 + 1x2^1 + 0x2^0 = 8 + 2 = 10_{dec}$$

L'intervallo di valori va da 0 a 2<sup>n</sup> 1

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

# 2.4 Arithmetic Logic Unit *Codifiche BU, BP*

| gruppi di 4 bit (rappresentare l' | informazione in Coded Decimal                    | dec 0 1 2 3 4 5 6 7 8 9 | BCD<br>0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001 |

|-----------------------------------|--------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|

| Lezione 6                         | Architettura degli Elaboratori - 1 - A. Sperduti |                         | Pagina 64                                                                           |

### 2.4 Arithmetic Logic Unit Bit di zero e di carry

- **Bit di zero**, vale 1 se tutti i bit del risultato sono a zero

- **Bit di carry**, vale 1 se il risultato di una operazione tra operandi senza segno supera il limite di valore consentito

- nelle somme rappresenta il riporto

- − nelle differenze vale −2<sup>n</sup>

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 65

## 2.4 Arithmetic Logic Unit

Operazioni tra interi senza segno

### 2.4 Arithmetic Logic Unit

Codifica dei dati interi con segno

|               | TIPO               | bit | rango                        |

|---------------|--------------------|-----|------------------------------|

| SB            | signed byte        | 8   | - 128 +127                   |

| SW            | signed word        | 16  | - 32768 +32767               |

| SD            | signed double word | 32  | $\sim - /+ 2.15 \times 10^9$ |

| $\mathbf{SQ}$ | signed quad word   | 64  | ~- /+ 9.22x10 <sup>18</sup>  |

| PD            | packed decimal     | 80  | - /+9,999 x10 <sup>18</sup>  |

|               |                    |     |                              |

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 67

# 2.4 Arithmetic Logic Unit Codifiche SB, SW, SD, SQ

Rappresentazione del numero in complemento a 2

Dato il numero ad n bit

$$A = a_{n-1} a_{n-2} \dots a_2 a_1 a_0$$

la  $\dot{i}$  esima cifra ha un peso di  $2^{i}$ , tranne quella per i = n-1, che vale  $-2^{n-1}$ , ad esempio

$$10110010_{\text{hin}} = -128 + 32 + 16 + 2 = -78_{\text{dec}}$$

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 68

# 2.4 Arithmetic Logic Unit Codifiche SB, SW, SD, SQ (segue)

Per passare da decimale (negativo) a complemento a 2:

- Rappresentare il numero (modulo) in binario con n-1 cifre

- Fare il complemento ad 1 dei singoli bit

- Incrementare di un'unità

- Il bit più significativo (MSb) diventa bit di segno

Il rango va da  $-2^{n-1}$  a  $+2^{n-1}-1$

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 69

### Esempio complemento a 2

- n=4

- - 3(3 usando n 1 bit) > 011

- 0011

- complemento a 1 bit/bit 1100

- aggiungere 1

1101

• controllo:- 8+4+1=- 3

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 70

# 2.4 Arithmetic Logic Unit Codifica PD

- Campo S, segno, un byte per il segno (negativo = *MSb* a 1)

- Campo **G**, grandezza, 9 byte in codifica *byte packed BCD*

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

### 2.4 Arithmetic Logic Unit Bit di segno e di overflow

- **Bit di segno** (*MSb*), vale 1 se il numero è negativo

- **Bit di overflow**, vale 1 se il risultato di un'operazione tra operandi con segno supera il rango consentito

- nelle somme vale 1 se e solo se i due operandi sono dello stesso segno ed il risultato è di segno opposto

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 72

### -38

| • 38 (7 bit) 32 + 4 + 2                     | 0100110  |

|---------------------------------------------|----------|

| •                                           | 00100110 |

| <ul> <li>complemento a 1 bit/bit</li> </ul> | 11011001 |

| • sommare 1                                 | 00000001 |

| •                                           | 11011010 |

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 74

### 2.4 Arithmetic Logic Unit

Operazioni tra interi con segno (comp. a 2)

$$(+89_{\rm dec}) + (-38_{\rm dec}) = 01011001 + \frac{11011010}{\rm s} = 001110011 \rightarrow +51_{\rm dec}$$

$$(+50_{\rm dec}) - (+85_{\rm dec}) = {\rm trasformata~in~somma} = (+50_{\rm dec}) + (-85_{\rm dec}) = 00110010 + \frac{10101011}{\rm s} = 0011011101 \rightarrow -35_{\rm dec}$$

Architettura degli Elaboratori - 1 - A. Sperduti

# 2.5 Arithmetic Logic Unit

Codifica dei numeri in virgola mobile (1)

- I **numeri reali** rappresentabili da un elaboratore sono un **sottinsieme finito** dei numeri razionali

- Si usa la notazione a virgola mobile:

$$N = +/- M \times B^E$$

- ►M, mantissa, numero razionale con segno

- ►E, esponente, numero intero con segno

- $\triangleright$ **B**, base, valore standard = 2

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 75

Lezione 6

### 2.5 Arithmetic Logic Unit

Codifica dei numeri in virgola mobile (2)

Lo standard ANSI/IEEE 754 usa la rappresentazione  $(-1)^S \times 1.M \times 2^{E-bias}$  a 3 campi:

- $\triangleright$ **S**, segno, su 1 bit (0  $\rightarrow$  numero positivo)

- ➤ M, mantissa, su m bit, normalizzata escludendo il bit più significativo che vale sempre 1

- ►E, esponente o caratteristica, su e bit, valutata in codifica ad eccesso 2<sup>e-1</sup> –1 (bias)

- $\triangleright$ Con precisione p = 1 + m + e

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 76

### 2.5 Arithmetic Logic Unit

Codifica dei numeri in virgola mobile (3)

TIPO

S e m bias

**SR** short real

32 1 8 23 127

$\sim 1.8 \times 10^{-38} < |x| < \sim 3.40 \times 10^{+38}$

LR long real

64 1 11 52 1023

$\sim 2.23 \times 10^{-308} < /x/ < \sim 1.80 \times 10^{+308}$

**XR** extended real 80 1 15 64 16383

$\sim 3.4 \times 10^{-4932} < |x| < \sim 1.2 \times 10^{+4932}$

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 77

### 2.5 Arithmetic Logic Unit

Codifica dei numeri in virgola mobile (4)

### Esempio

Il valore in codifica SR (single-precision)

dove S = 0,  $E = 10000110 = 134_{dec}$ , e

$\mathbf{M} = 000000010...0_{\mathrm{IEEE754}} = 00000001_2/100000000_2 = 0.00390625$  (equivalente a  $2^{-8}$ , con le cifre in mantissa aventi peso negativo) corrisponde al valore decimale:

$x = (-1)^0 \times 1.00390625 \times 2^{134-127} = 1.00390625 \times 128 = 128.5$

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 78

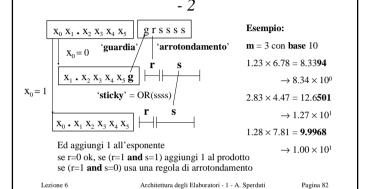

## 2.5 Arithmetic Logic Unit

Somma di numeri in virgola mobile

Dati  $\mathbf{X} = \mathbf{X}_{s} \times \mathbf{X}_{m_{v}} \times 2^{e_{x}} e \mathbf{Y} = \mathbf{Y}_{s} \times \mathbf{Y}_{m_{v}} \times 2^{e_{y}} (|\mathbf{X}| < |\mathbf{Y}|)$

- Calcolare  $n = e_y e_x$

- Spostare  $\mathbf{X}_{\mathbf{m_v}}$  n volte a destra, ottenendo  $\mathbf{X'}_{\mathbf{m}} = \mathbf{X}_{\mathbf{m_v}}/2^{\mathbf{n}}$

- Calcolare  $Z_m = X'_m + Y_{m_w}$  e normalizzare ad m bit

- Fissare  $e_z = e_y$

- Calcolare Z<sub>s</sub> (il segno del risultato)

- Il risultato vale  $X + Y = Z_s \times Z_m \times 2^e_z$

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

# 2.5 Arithmetic Logic Unit Esempio

A =

$$1.10011_2 \times 2^0$$

B =  $1.10001_2 \times 2^5$

A + B =  $1.10011$  + .0000110001 = 1.10100 10001 = \*sticky bits' usati per l'arrotondamento 1.10101<sub>2</sub> × 2<sup>0</sup> dopo l'arrotondamento

Vedi: Hennessy & Patterson sezione A-5

ezione 6 Architettura degli Elaboratori - 1 - A. Sperduti

## 2.5 Arithmetic Logic Unit

Pagina 80

Pagina 81

Moltiplicazione di numeri in virgola mobile

- 1

Precisione semplice con mantissa intera

$1 \times 10000110 = (s_1 \times s_2) \times 2(e_{1} + e_{2} - bias)$

Vedi: Hennessy & Patterson sezione A-4

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti

## 2.5 Arithmetic Logic Unit

Moltiplicazione di numeri in virgola mobile

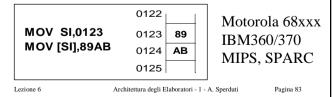

# 2.5 Arithmetic Logic Unit Memorizzazione dei dati Big Endian

- Big Endian: si memorizzano i byte più significativi del dato a partire dagli indirizzi inferiori

- L'indirizzo del dato è quello dell'MSB (big end)

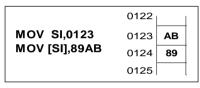

# 2.5 Arithmetic Logic Unit

Memorizzazione dei dati Little Endian

- Little Endian: si memorizzano i byte meno significativi dell'informazione a partire dagli indirizzi inferiori

- L'indirizzo del dato è quello dell'LSB (small end)

Intel x86 DEC Vax

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 84

# 2.6 Bus, instradatori e buffer Modalità punto-a-punto

Address bus

reg. stack

reg. index

DB buffer

Data Bus

Architettura degli Elaboratori - 1 - A. Sperduti

prefetch

registro 1

registro N

reg.stato

Lezione 6

Bus e buffer

buffer

bus interno 1

bus interno 2

Pagina 86

Pagina 87

• Un collegamento tra tutti i possibili percorsi

- Complessità di sincronizzazione

- Massima flessibilità

- Grande complessità realizzativa

Architettura degli Elaboratori - 1 - A. Sperduti

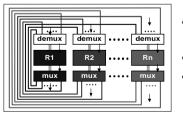

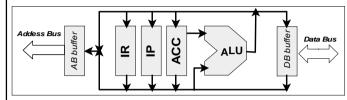

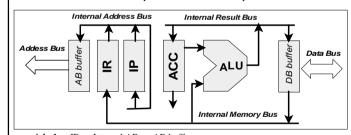

### 2.6 Bus, instradatori e buffer

- Le tecniche di trasferimento dati all'interno della CPU hanno grande influenza sulle prestazioni generali

- − Efficienza: ~ numero di cicli per istruzione; grado di parallelismo interno

- Almeno 3 architetture di trasferimento:

- Punto-a-punto, bus singolo, bus multiplo

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

### 2.6 Bus, instradatori e buffer Modalità a bus singolo

• Un solo percorso, condiviso temporalmente

- Minore complessità

- Minore flessibilità

- Più fasi operative

- · Possibilità di broadcast

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 88

### 2.6 Bus, instradatori e buffer Modalità a bus multipli

- Compromesso tra le soluzioni punto a punto e bus singolo

- Molteplici percorsi, sia generali che dedicati

- Maggior grado di parallelismo interno

- Il numero ottimale di bus dipende dal tipo di istruzioni e di indirizzamenti desiderati

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 89

### 2.6 Bus, instradatori e buffer Esempio a bus singolo

Fase di esecuzione dell'istruzione ADD ACC, Mem[indirizzo]

ciclo 1 IP ⇒ Internal Bus ⇒ AB buffer

ciclo i lettura di **Mem**oria all'**indirizzo** specificato

*ciclo j+1* DB buffer  $\Rightarrow$  Internal Bus  $\Rightarrow$  ALU<sub>op</sub>, ACC  $\Rightarrow$  ALU<sub>op</sub>, ADD

*ciclo j*+2  $ALU_{res} \Rightarrow Internal Bus \Rightarrow ACC$

ezione 6 Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 90

### 2.6 Bus, instradatori e buffer Esempio a bus multiplo

*ciclo 1* IP  $\Rightarrow$  Internal AB  $\Rightarrow$  AB buffer

ciclo j lettura di Memoria all'indirizzo specificato

*ciclo j+1* DB buffer  $\Rightarrow$  Internal MB  $\Rightarrow$  ALU<sub>op2</sub>, **ACC**  $\Rightarrow$  ALU<sub>op1</sub>,

**ADD**,  $ALU_{res} \Rightarrow Internal RB \Rightarrow ACC$

one 6 Architettura degli Elaboratori - 1 - A. Spe

### 2.6 Parte controllo (control path)

- Già discussa come 'PC microprogrammata'

- Ad ogni **istruzione** della CPU corrisponde un **microprogramma** memorizzato in una memoria di controllo (*equivalente, ma non uguale, alla ROM*)

- L'uso di microprogrammazione **facilita** la progettazione e l'ottimizzazione della CPU

- L'esecuzione via microistruzioni è generalmente più **lenta** dell'implementazione hardware

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 93

### 2.7 Instruction set 1

- L'instruction set specifica le **operazioni esterne** della CPU

- Le istruzioni possono prevedere **operandi** con varie modalità di localizzazione

- Le istruzioni possono avere **vari formati** e **diversa durata**

- Il tipo di istruzioni previsto da un instruction set determina il costo e le prestazioni della CPU

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 94

### 2.7 Instruction set 2

- Un instruction set definisce (corrisponde ad) una particolare **architettura** di CPU

- Architettura a pila (stack)

- Architettura ad accumulatore

- Architettura a registri generali

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

### 2.7 Architettura a pila

- Gli operandi sono assunti essere presenti in testa ad una particolare zona di memoria detta 'pila di sistema'

- Le operazioni di calcolo sono precedute da inserimento di operandi (PUSH) in pila e seguite da prelievo del risultato (POP) dalla pila

- Architettura arcaica e poco efficace

- Programmazione verbosa

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 96

### 2.7 Architettura ad accumulatore

- Uno degli operandi dell'istruzione è assunto trovarsi sempre in un registro speciale detto 'accumulatore'

- Gli altri operandi sono generalmente localizzati in memoria

- Architettura arcaica e poco efficace

- Programmazione concisa

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

agina 97

### 2.7 Architettura a registri generali

- Gli operandi sono tutti espliciti

- Gli operandi sono localizzati in **memoria** o in **registri generali**

- Esiste una vasta gamma di modalità di localizzazione (indirizzamento) degli operandi

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 98

### 2.7 Esempio

### $A + B \rightarrow C$

#### Architettura a pila

Push A | Push B | Add | Pop C

$A {\rightarrow} Stack \mid B {\rightarrow} Stack \mid < risultato > {\rightarrow} Stack \mid Stack {\rightarrow} C$

#### Architettura ad accumulatore

Load A | Add B | Store C

$A \rightarrow Acc \mid Acc+B \rightarrow Acc \mid Acc \rightarrow C$

#### Architettura a registri generali

$Load\ R1,\!A\mid Load\ R2,\!B\mid Add\ R1,\!R2,\!R3\mid Store\ C,\!R3$

$A \rightarrow R1 \mid B \rightarrow R2 \mid R1+R2 \rightarrow R3 \mid R3 \rightarrow C$

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

### 2.7 Ulteriore classificazione 1

Esistono **tre** sottoclassi di architetture a registri generali

- Registro-registro (Load/Store)

- Tutti gli operandi sono su registro. Gli accessi a memoria si effettuano con **Load** (prelievo) e **Store** (deposito)

- Memoria-registro

Prevedono operazioni con alcuni operandi in memoria ed altri su registro

- Memoria-memoria

Prevedono operazioni che prelevano operandi in memoria e restituiscono il risultato in memoria

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 100

### 2.7 Ulteriore classificazione 2

- Architetture commerciali di tipo 1 (Load/Store)

- SPARC, MIPS, PowerPC

- Architetture commerciali di tipo 2 (memoria/registro)

- Intel x86, Motorola 68k

- **Non** esistono architetture commerciali di tipo 3 (memoria/memoria)

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 10

# 2.7 Architettura Load/Store (RISC)

- Necessita di poche istruzioni, con formato molto semplice ed uniforme

- Le istruzioni hanno tempi di esecuzione molto simili tra loro

- Facilita il compito dei generatori automatici di codice macchina (compilatori)

- Nota sotto il nome di architettura **RISC** (Reduced Instruction Set Computer)

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 102

### 2.7 Architettura CISC

- Alternativa alla regolarità dell'architettura RISC è la cosiddetta architettura CISC (Complex Instruction Set Computer), che utlizza istruzioni a formato variabile, con grande potenza espressiva e tempi di esecuzioni variabili e spesso elevati

- L'architettura Intel x86 è di tipo CISC

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

gina 103

### 2.7 Modalità di indirizzamento

| Registro          | Add R1,R2               | [R1] <b>←</b> [R1]+[R2]                   |

|-------------------|-------------------------|-------------------------------------------|

| Immediata         | Add R1,K                | $[R1] \leftarrow [R1] + K$                |

| Displacement      | Add R1,K,[R2]           | $[R1] \leftarrow [R1] + Mem[K + [R2]]$    |

| Indiretta         | Add R1,[R2]             | $[R1] \leftarrow [R1] + Mem[[R2]]$        |

| Indicizzata       | Add R1,[R2+R3]          | $[R1] \leftarrow [R1] + Mem[[R2] + [R3]]$ |

| Assoluta          | Add R1,[K]              | $[R1] \leftarrow [R1] + Mem[K]$           |

| Memoria indiretta | Add R1,@[R2]            | $[R1] \leftarrow [R1] + Mem[Mem[[R2]]]$   |

|                   |                         |                                           |

| Lezione 6         | Architettura degli Elab | ooratori - 1 - A. Sperduti Pagina 104     |

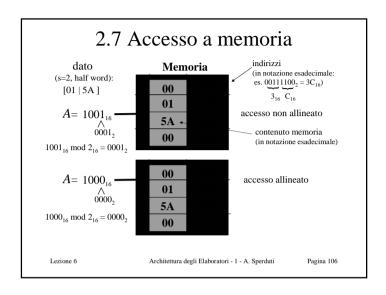

### 2.7 Accesso a memoria

- · A questo livello, la memoria viene vista come un array di byte

- Per ogni richiesta di un dato ad un certo indirizzo, la CPU ottiene un numero di byte determinato dall'ampiezza del Data Bus e dalle modalità di allineamento dei dati in memoria

- Un accesso ad un dato (composto da s byte) all'indirizzo A si dice **allineato** se  $A \mod s = 0$

| Formato del dato     | Allineato (ultimi 3 bit di A)             | Non allineato       |

|----------------------|-------------------------------------------|---------------------|

| byte                 | 0,1,2,3,4,5,6,7                           | mai                 |

| half word (2 byte)   | 0,2,4,6                                   | 1,3,5,7             |

| word (4 byte)        | 0,4                                       | 1,2,3,5,6,7         |

| double word (8 byte) | 0                                         | 1,2,3,4,5,6,7       |

| Lezione 6            | Architettura degli Elaboratori - 1 - A. S | Sperduti Pagina 105 |

### 2.7 Accesso a memoria

- Memoria non allineata (Intel x86)

- Accessi facilitati ed ottimizzati

- Maggiore complessità di progettazione

- Memoria allineata (SPARC, Motorola 68k)

- Accesso più complesso a dati non allineati

- Richiede compilatori efficienti per preservare capacità di accesso adeguata a dati non allineati

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 107

### 2.7 Tassonomia di istruzioni

| Tipo                  | Esempi                                                      |

|-----------------------|-------------------------------------------------------------|

| aritmetiche e logiche | aritmetica intera e operazioni logiche:                     |

|                       | add, and, subtract, or                                      |

| trasferimento dati    | trasferimento dati da/per memoria/registri:                 |

|                       | load, store                                                 |

| controllo             | branch, jump, chiamata e ritorno da procedure,              |

|                       | traps                                                       |

| sistema               | chiamate di sistema operativo, istruzioni per la            |

|                       | gestione della memoria virtuale                             |

| virgola mobile        | operazioni in virgola mobile:                               |

|                       | add, multiply                                               |

| decimale              | operazioni decimali: decimal add, decimal                   |

|                       | multiply, decimal-to-character conversions                  |

| stringa               | spostamento, comparazione, ricerca di stringhe              |

| grafica               | operazioni su pixel, operazioni di                          |

|                       | compressione/decompressione                                 |

| Lezione 6             | Architettura degli Elaboratori - 1 - A. Sperduti Pagina 108 |

## 2.7 Istruzioni più usate (80x86)

| istruzione            | percentuale di uso |

|-----------------------|--------------------|

| load                  | 22%                |

| branch condizionale   | 20%                |

| compare               | 16%                |

| store                 | 12%                |

| add                   | 8%                 |

| and                   | 6%                 |

| sub                   | 5%                 |

| spostamento reg./reg. | 4%                 |

| call                  | 1%                 |

| return                | 1%                 |

| Totale                | 96%                |

## 2.7 Altri tipi di istruzioni

- Trasferimento di controllo

- Operanti su Instruction Pointer (IP), detto anche Program Counter (PC)

- Operazioni su stack

- Push, Pop

- Operazione specializzate

- Aritmetica BCD, trattamento I/O

Lezione 6 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 110

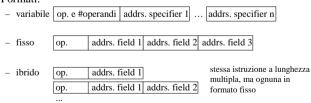

### 2.7 Formato delle istruzioni

- Come vengono codificate in binario le istruzioni ?

- Bisogna specificare:

- di quale operazione si tratta (opcode);

- il tipo/i di indirizzamento di memoria usato/i (address mode(s))

- Formati:

Lezione 6

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 111

Lezione 6

## 2.7 Formato delle istruzioni

```

• Esempi:

- variabile (VAX):

addl3 r1,737(r2),(r3)

- fisso (DLX)

add r1,r2,r3

- ibrido (80x86)

fadd

operandi e risultato in stack

fadd st(i)

un operando in registro i sotto la stack ...

fadd mem32

un operando è una cella di memoria a 32 bit ...

Architettura degli Elaboratori - 1 - A. Sperduti

Lezione 6

Pagina 112

```