#### **MIPS**

- Architettura RISC

- Architettura molto regolare con insieme di istruzioni semplice e compatto

- Architettura progettata per una implementazione efficiente di pipeline (lo vedremo più avanti)

- Codifica delle istruzioni omogenea: 32 bit

- Co-processore per istruzioni a virgola mobile e gestione delle eccezioni

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 65

### **MIPS**

#### Dati e modi di indirizzamento

- Registri possono essere caricati con byte, mezze parole, e parole (riempiendo con 0 quando necessario o estendendo, cioè replicando, il segno sui bit non coinvolti del registro)

- Modalità di indirizzamento ammesse (con campi di 16 bit):

- Immediata es. add \$2, \$2, 0004

- Displacement es. sw \$1,000c(\$1)

- Altre modalità derivabili:

- Indiretta (displacement a 0) es. sw \$2,0000(\$3)

- Assoluta (registro 0 come registro base) es. lw \$1,00c4(\$0)

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 67

#### **MIPS**

### Registri

- 32 registri di 32 bit (registro 0 contiene sempre il valore 0)

- Architettura Load / Store

- Istruzioni di trasferimento per muovere i dati tra memoria e registri

- Istruzioni per la manipolazione di dati operano sui valori dei registri

- Nessuna operazione memoria ↔ memoria

- Quindi: le istruzioni operano su registri (registro i riferito con \$i)

- Esempio: add \$0, \$1, \$2

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 66

#### **MIPS**

#### Formato Istruzioni

- 32 bit per tutte, 3 formati diversi (formato R, formato I, formato J)

- Formato R (registro)

Es: 0x02484020 (add \$8,\$18,\$8

$[R8] \leftarrow [R18] + [R8])$

op

rs

rt

rd

shamt

funct

000000

10010

01000

01000

00000

100000

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

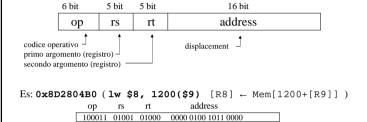

#### **MIPS**

#### Formato Istruzioni

• Formato I (istruzioni load / store)

Architettura degli Elaboratori - 1 - A. Sperduti

# Central Processing Unit

La CPU

Lezione 5

Logica operativa (data path)

Registri

Circuiti aritmetici dedicati

Arithmetic Logic Unit, ALU

Bus, instradatori e buffer

Logica di controllo (control path)

Set di istruzioni

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 71

Pagina 69

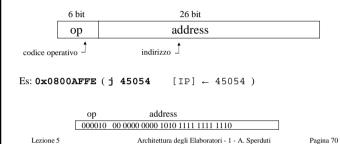

#### **MIPS**

#### Formato Istruzioni

• Formato J (istruzioni jump)

### Unità centrale

La CPU è suddivisibile in due blocchi funzionali:

- Sottosistema gestione dati: data path (logica operativa), adibito alla memorizzazione, all'elaborazione ed all'analisi dei dati interni alla CPU

- Sottosistema gestione istruzioni: control path (logica di controllo), che ha il compito di decodificare ed interpretare le istruzioni, e di far eseguire alla logica operative le operazioni necessarie per la loro esecuzione

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

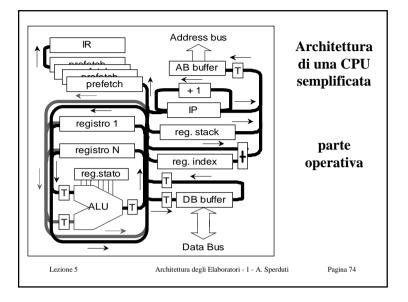

# Parte operativa (data path)

La parte operativa è costituita da vari elementi:

- Registri

- Circuiti combinatori elementari

- Arithmetic Logic Unit

- Aree di memoria di lavoro (buffer)

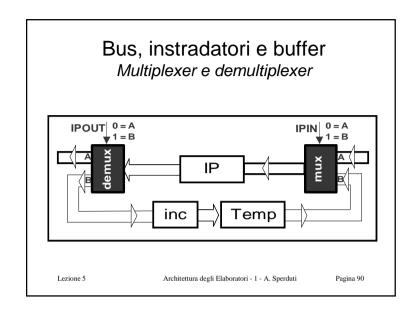

- Instradatori (multiplexer e demultiplexer)

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 73

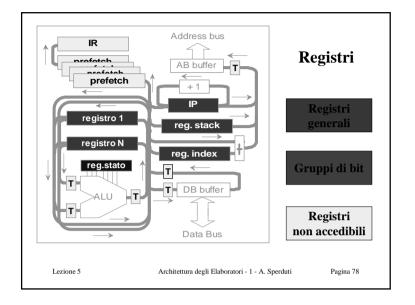

# Registri

- Piccole memorie temporanee molto veloci basate su componenti statici (*flip flop*)

- In numero e dimensioni variabili

- Un maggior numero di registri permette di:

- Ridurre il numero di accessi alla memoria esterna

- Esecuzione più veloce

- Ridurre la complessità operativa delle istruzioni

- Compilatore più semplice

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 75

# Registri (segue)

I registri possono avere ciascuno una funzione specifica o essere di utilizzo generale:

- **Registri dedicati** (p.es., accumulatore): ad uso limitato ma con prestazioni migliori

- **Registri generali:** semplificano la parte controllo e l'ottimizzazione da parte dei compilatori; facilmente scalabili

La soluzione più conveniente è quella mista

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

# Registri (segue)

#### I registri generali

- A disposizione del programmatore

- A dimensione variabile 8, 16, 32, 64 bit

- Utilizzati per la memorizzazione dati, per il calcolo di indirizzi, per operazioni aritmeticologiche

- Possono avere compiti specifici

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 77

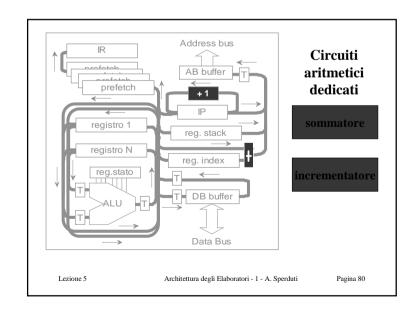

## Circuiti aritmetici dedicati

Finalizzati esclusivamente a permettere una maggiore velocità dell'ALU, p.es.:

- Incrementatore

- Per far avanzare l'Instruction Pointer

- Per particolari istruzioni auto-aggiornanti

- Sommatore

- Per calcolare l'indirizzo di un operando

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

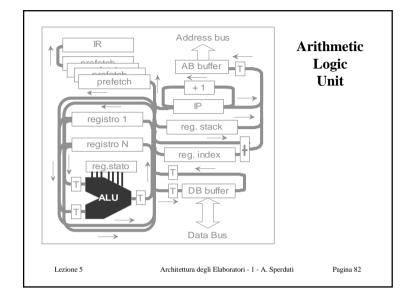

# Arithmetic Logic Unit

- Rete combinatoria multi-funzione, in grado di effettuare operazioni aritmetiche e/o logiche su uno o due operandi

- Acquisisce ed aggiorna una serie di bit di stato, detti 'flag', p.es.: zero, carry, overflow, segno, ... (controllo residuo)

- Esegue operazioni di spostamento di bit, con shifter dedicati

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 81

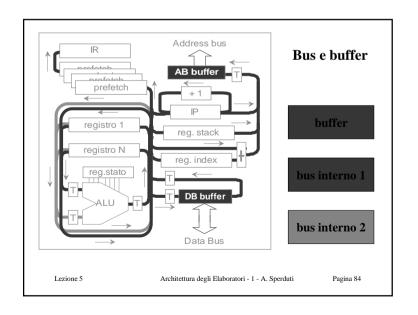

### Bus, instradatori e buffer

- Le tecniche di trasferimento dati all'interno della CPU hanno grande influenza sulle prestazioni generali

- Efficienza: ~ numero di cicli per istruzione; grado di parallelismo interno

- Almeno 3 architetture di trasferimento:

- Punto-a-punto, bus singolo, bus multiplo

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

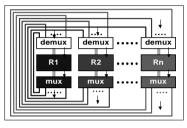

# Bus, instradatori e buffer *Modalità punto-a-punto*

• Un collegamento tra tutti i possibili percorsi

- Complessità di sincronizzazione

- · Massima flessibilità

- Grande complessità realizzativa

Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 85

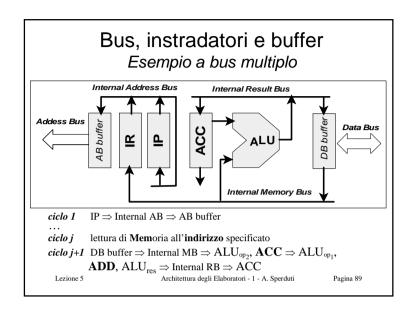

## Bus, instradatori e buffer Modalità a bus multipli

- Compromesso tra le soluzioni punto-a-punto e bus singolo

- Molteplici percorsi, sia generali che dedicati

- Maggior grado di parallelismo interno

- Il numero ottimale di bus dipende dal tipo di istruzioni e di indirizzamenti desiderati

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 87

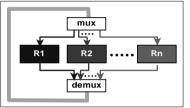

### Bus, instradatori e buffer Modalità a bus singolo

• Un solo percorso, condiviso temporalmente

- Minore complessità

- Minore flessibilità

- Più fasi operative

- Possibilità di broadcast

Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 86

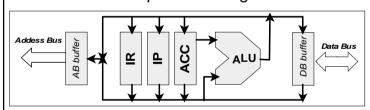

### Bus, instradatori e buffer Esempio a bus singolo

Fase di esecuzione dell'istruzione ADD ACC, Mem[indirizzo]

*ciclo 1* IP  $\Rightarrow$  Internal Bus  $\Rightarrow$  AB buffer

ciclo j lettura di Memoria all'indirizzo specificato

$\textit{ciclo j+1} \quad \text{DB buffer} \Rightarrow \text{Internal Bus} \Rightarrow \text{ALU}_{op_2}, \textbf{ACC} \Rightarrow \text{ALU}_{op_1}, \textbf{ADD}$

*ciclo j*+2  $ALU_{res} \Rightarrow Internal Bus \Rightarrow ACC$

ezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 88

# Parte controllo (control path)

- Implementazione hardware (cablata) o 'microprogrammata'

- Nel caso di microprogrammazione, ad ogni **istruzione** della CPU corrisponde un **microprogramma** memorizzato in una memoria di controllo (*equivalente*, *ma non uguale*, *alla ROM*)

- L'uso di microprogrammazione **facilita** la progettazione e l'ottimizzazione della CPU

- L'esecuzione via microistruzioni è generalmente più **lenta** dell'implementazione hardware

Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 91

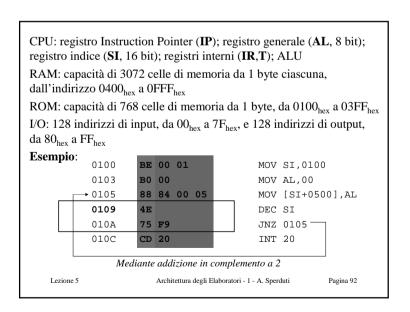

#### Architettura semplificata R/W 1 0400 - 0FFF 0100 - 03FF IP 0109 05FF XX ⊬ [01] IR B0 floppy Z 8 [02] 0600 00 010A 75 AL 00 0601 xx 010BF9 0602 xx 010C CD xxxx .... .. [81] .... . . 04FF xx 03FF xx € [82] floppy SI 0100 [83] hard disk xx RAM ROM ALU CPU **Read memory**: la ROM, attivata dall'indirizzo presente in AB, seleziona la sua cella di indirizzo 0109 e, dato il valore della linea R/W (=1), pone il contenuto della cella in DB Architettura degli Elaboratori - 1 - A. Sperduti Pagina 94

# Architettura semplificata

**Decodifica**: il codice operativo dell'istruzione corrente (**4E**) informa la CPU che essa deve decrementare di 1 il contenuto di SI.

L'istruzione è lunga un solo byte, che ne rappresenta il **codice operativo**.

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

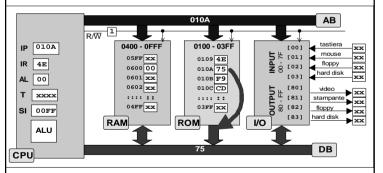

#### Architettura semplificata IP 010A mouse xx 0109 4E IR 4E floppy 010A 75 nard disk 0601 xx 010B F9 AL 00 010C CD xxxx 04FF<sub>XX</sub> 03FF xx floppy hard disk ROM Execute (1): la CPU invia all'ALU il contenuto di SI (0100) ed impone l'operazione di decremento di un'unità. Il risultato (00FF) viene salvato nello stesso registro SI. Architettura degli Elaboratori - 1 - A. Sperduti Pagina 97

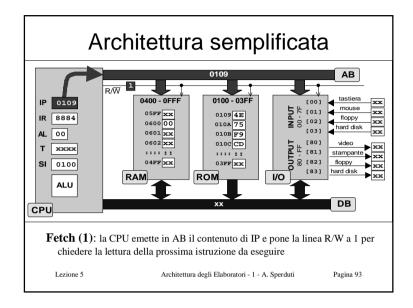

#### Architettura semplificata AB 0400 - 0FFF 0100 - 03FF IP 010A 05FFxx 0109 4E 0600 00 010A 75 **AL** 00 0601 xx 010BF9 0602 xx 010C CD xxxx .... . . stampante .... . . 04FFxx 00FF 03FF xx 2 [82] floppy [83] hard disk ROM ALU DB CPU Fetch (1): la CPU emette in AB il contenuto di IP e pone la linea R/W a 1 per leggere la prossima istruzione da eseguire Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 99

# Architettura semplificata

L'istruzione DEC SI è stata completata mediante :

- Fetch (fase 1): emetti IP in AB

- · Richiesta di lettura in memoria

- **Fetch** (fase 2): scrivi in IR il valore fornito da DB, incrementa IP, decodifica l'istruzione in IR

- Execute (fase 1): decrementa SI

- In questo caso non sono necessarie altre sottofasi

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 98

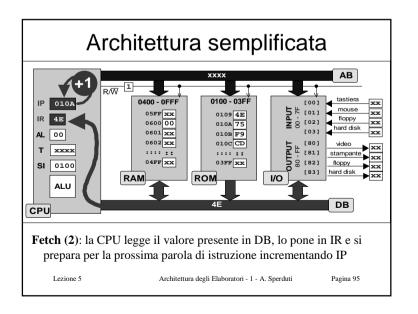

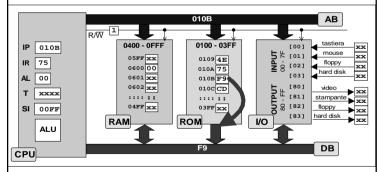

# Architettura semplificata

**Read memory**: la ROM, attivata dall'indirizzo presente in AB, seleziona la sua cella di indirizzo 010A e, dato il valore della linea R/W (=1), pone il contenuto della cella in DB

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

#### Architettura semplificata 0100 - 03FF 0400 - 0FFF 0109 4E floppy 010A 75 0601 xx 010B F9 00 0602 xx 010C CD xxxx .... ... .... :: 04FF<sub>XX</sub> 03FF xx floppy SI OOFF hard disk ROM RAM ALU DB CPU Fetch (2): la CPU legge il valore presente in DB, lo pone in IR e si prepara per la prossima parola di istruzione incrementando IP Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 101

#### Architettura semplificata AB R/W 1 0400 - 0FFF 0100 - 03FF 010B 0109 4E IR 75 floppy 0600 00 010A 75 AL 00 0601 xx 010BF9 0602 xx 010C CD xxxx ..... :::: :: stampante 04FF<sub>XX</sub> 03FF xx floppy 00FF hard disk RAM ROM ALU DB CPU Execute (1): l' istruzione ha 1 operando, dunque la CPU emette il contenuto di IP in AB e pone la linea R/W a 1, per leggere l'operando (displacement) Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 103

# Architettura semplificata

**Decodifica**: il codice operativo dell'istruzione corrente (75) informa la CPU che l'istruzione è condizionata dal valore del bit di zero (**flag Z**).

$Z=1 \rightarrow prosegui normalmente (jump if not zero)$

**Z**=0 → somma l'operando (*displacement*) ad IP L'operazione si può effettuare su 16 bit in complemento a 2 (oppure sugli 8 bit della parte bassa dei dati trascurando l'eventuale riporto)

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 102

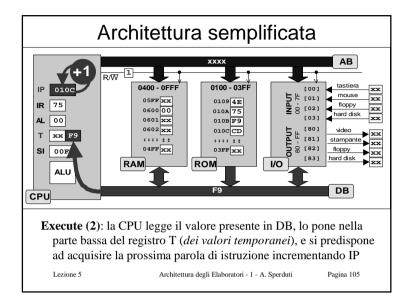

# Architettura semplificata

**Read memory**: la ROM, attivata dall'indirizzo presente in AB, seleziona la sua cella di indirizzo 010B e, dato il valore della linea R/W (=1), pone il contenuto della cella in DB

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

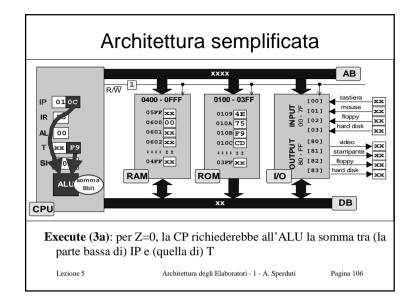

#### Architettura semplificata 0400 - 0FFF 0100 - 03FF 0109 4E IR 75 floppy 0600 00 010A 75 0601 xx **AL** 00 010BF9 0602 xx 010C CD T xxF9 stampante xx .... .. .... :: SI 00FF 04FF<sub>XX</sub> 03FF xx F821 floppy hard disk RAM ROM DB Execute (3b): la CPU poi scriverebbe il risultato nel(la parte bassa del) registro IP (trascurando eventuale riporti), determinando cosi' l'indirizzo non consecutivo dell'istruzione successiva (JUMP, salto) Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 107

# Architettura semplificata

L'istruzione JNZ F9 è stata completata mediante:

- Fetch (1): emetti IP in AB

- Richiesta di lettura in memoria

- **Fetch**(2): scrivi in IR il valore in DB, incrementa IP, effettua decodifica

- Execute (1): emetti IP in AB

- Richiesta di lettura in memoria

- Execute (2): scrivi in T il valore in DB, incrementa IP

- Execute (3): verifica Z, se Z=0 allora  $IP + T \rightarrow IP$

Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti Pagina 108

## Altro Esempio

#### Architettura con accumulatore (Assembler 6502):

• il programma (notazione esadecimale: (hex)adecimal)

| INDI<br>0100<br>0102 | 9A 2 | TENUTO PROGRAM<br>23 LDA #23<br>13 20 ADC \$204 | carica il byte con valore 23 <sub>hex</sub> nell'accumulatore |

|----------------------|------|-------------------------------------------------|---------------------------------------------------------------|

| 0105                 | 84 4 | 4 20 STA \$2044                                 | memorizza il risultato all'indirizzo 2044h                    |

• la memoria (byte per byte): memorizzazione dati Little Endian

| Lezione 5 |          | Architettura degli Elaboratori - 1 - A. Sperduti | Pagina 109 |

|-----------|----------|--------------------------------------------------|------------|

| 0108      |          |                                                  |            |

| 0107      | 20       |                                                  |            |

| 0106      | 44       |                                                  |            |

| 0105      | 84       |                                                  |            |

| 0104      | 20       |                                                  |            |

| 0103      | 43       |                                                  |            |

| 0102      | 8A       |                                                  |            |

| 0101      | 23       |                                                  |            |

| 0100      | 9A       |                                                  |            |

| 00FF      |          |                                                  |            |

| Indirizzi | CONTENUT | O                                                |            |

# Altro Esempio

#### Sequenza fetch/execute:

IP = 0103 Pone il

Pone il contenuto di IP nell'address bus e la linea R/W ad 1. Carica il byte =  $43_{hex}$  nel registro dati. Incrementa IP (IP=0104). Muove il dato dal registro dati al byte meno significativo di un registro temporaneo T (di 2 byte).

IP = 0104

Pone il contenuto di IP nell'address bus e la linea R/W ad 1. Carica il byte =  $20_{\text{hex}}$  nel registro dati. Incrementa IP (IP=0105). Muove il dato dal registro dati al byte piu' significativo del registro temporaneo T. Muove il contenuto del registro temporaneo nell'address bus e pone la linea R/W ad 1. Carica il byte contenuto nella locazione  $2043_{\text{hex}}$  nel registro dati. Somma il dato ad ACC. Setta flag di riporto (carry) se la somma genera overflow.

Lezione 5

Architettura degli Elaboratori - 1 - A. Sperduti

Pagina 111

# Altro Esempio

#### Sequenza fetch/execute:

IP = 0100 Pone il contenuto di IP nell'address bus e la linea R/W ad 1.

Carica il codice operativo (opcode)  $9A_{hex}$  nel registro dati dal data bus. Incrementa IP (IP=0101). Muove il dato dal registro dati al registro IR. Decodifica il codice operativo (la decodifica

segnala che è necessario un operando).

IP = 0101 Pone il contenuto di IP nell'address bus e la linea R/W ad 1.

Carica il byte = 23<sub>hex</sub> nel registro dati. Incrementa IP (IP=0102;

punta alla istruzione ADC \$2043). Muove il dato

nell'accumulatore ACC.

IP = 0102 Pone il contenuto di IP nell'address bus e la linea R/W ad 1.

Carica il codice operativo  $8A_{\text{hex}}$  nel registro dati dal data bus.

Incrementa IP (IP=0103). Muove il dato dal registro

dati al registro IR. Decodifica il codice operativo (la decodifica segnala che i prossimi 2 byte in memoria contengono

l'indirizzo del dato da utilizzare).

Lezione 5 Architettura degli Elaboratori - 1 - A. Sperduti